Your Name (first last)

# EECS 151/251A Fall 2020 Midterm 1

October 6, 2020

| Question          | 1  | 2  | 3  | 4  | 5  | Total |

|-------------------|----|----|----|----|----|-------|

| Sugg. time (mins) | 15 | 15 | 15 | 20 | 15 | 80    |

| Max. points       | 15 | 15 | 16 | 18 | 16 | 80    |

#### Exam Notes:

Between 3:30pm PST and 3:40pm PST, you may set up your recording, print the exam or transfer it to another device as needed, etc., but you may NOT begin working.

You have 80 minutes to work, starting at 3:40pm PST and ending at 5:00pm PST.

Please keep the Google Doc page that you received at 3:30pm PST open during the exam. It contains the following information:

- 1. A link to the exam PDF

- 2. A form for exam questions and reporting technical difficulties

- 3. A form for your exam recording link

- 4. Gradescope submission link

- 5. Exam errata

- 6. Summary of exam steps

# Problem 1: It's all logical... [15 points, 15 minutes]

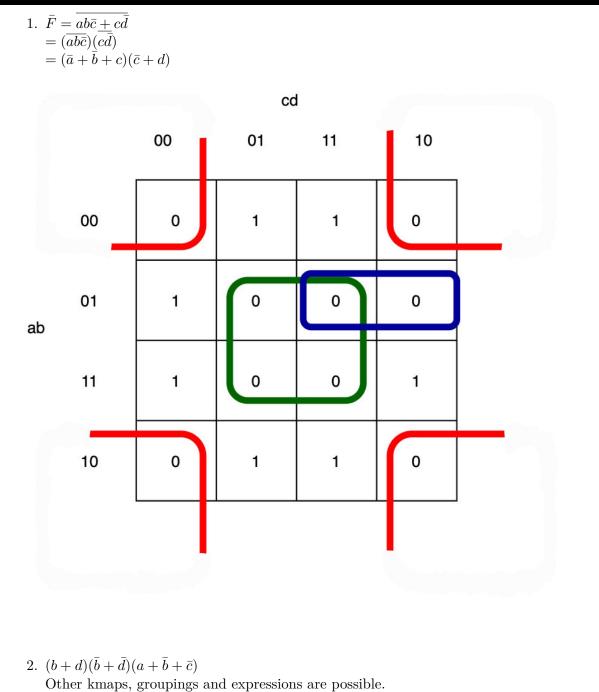

(a) Given  $F = \overline{(\bar{a} + c)}b + c\bar{d}$ , use De Morgan's law to derive  $\bar{F}$ . Write the equation in productof-sums form.

(b) Use a K-map to simplify the following expression and leave in product-of-sums form:

$F = \bar{b}d + b\bar{c}\bar{d} + ab\bar{c}\bar{d} + abc\bar{d}$

Your expression should have no more than 5 terms. Include the K-map in your solution.

(c) How many unique truth tables are there with m inputs and n outputs?

Answer: \_\_\_\_\_

3. There are  $2^m$  rows in a truth table of m inputs. Each row has  $2^n$  possible values. So there are  $(2^n)^{(2^m)}$  combinational logic circuits in total.

# Problem 2: VERIfiably LOGical [15 points, 15 minutes]

Consider the following Verilog module:

```

module my_module(

input clk, load,

input [2:0] in,

output reg [2:0] out

);

always @(posedge clk) begin

if (load) out <= in;</pre>

else begin

out[0] = -out[0];

if (out[0])

out[1] <= ~out[1];</pre>

if (out[0] & out[1])

out[2] <= ~out[2];</pre>

end

end

endmodule

```

(a) Draw the circuit diagram for this design. You may use the module inputs (e.g. in[0]), constants, muxes, inverters, and/or 2-input logic gates.

(b) Say we load 3'b011 using our load and in input signals. We then deassert load. What is the value of out for the first 6 cycles?

| Cycle | out |

|-------|-----|

| 0     | 011 |

| 1     |     |

| 2     |     |

| 3     |     |

| 4     |     |

| 5     |     |

Now, consider this similar module:

```

module my_module(

input clk, load,

input [2:0] in,

output reg [2:0] out

);

always @(posedge clk) begin

if (load) out = in;

else begin

out[0] = ~out[0];

if (out[0])

out[1] = -out[1];

if (out[0] & out[1])

out[2] = -out[2];

end

end

endmodule

```

(c) Say we load 3'b011 again using our load and in input signals. What is the value of out for the first 6 cycles?

| Cycle | out |

|-------|-----|

| 0     | 011 |

| 1     |     |

| 2     |     |

| 3     |     |

| 4     |     |

| 5     |     |

# Solution:

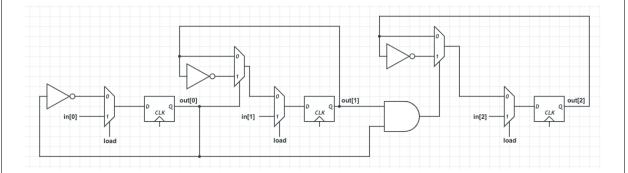

(a) During the exam, a clarification was made that all assignments in this part were meant to be non-blocking. However, credit was awarded for those who solved the question as written.

Here is the circuit diagram for the corrected (non-blocking) code:

The code as written produces a slightly different circuit (assume the rest of the circuit is the same as in the previous diagram).

(b) With the corrected code (all assignments non-blocking), this Verilog describes a counter.

| Cycle | out |

|-------|-----|

| 0     | 011 |

| 1     | 100 |

| 2     | 101 |

| 3     | 110 |

| 4     | 111 |

| 5     | 000 |

| Cycle | out |

|-------|-----|

| 0     | 011 |

| 1     | 010 |

| 2     | 101 |

| 3     | 100 |

| 4     | 111 |

| 5     | 110 |

As written (out[0] = -out[0]):

(c) With all assignments blocking, the module now describes a downward counter.

| Cycle | out |

|-------|-----|

| 0     | 011 |

| 1     | 010 |

| 2     | 001 |

| 3     | 000 |

| 4     | 111 |

| 5     | 110 |

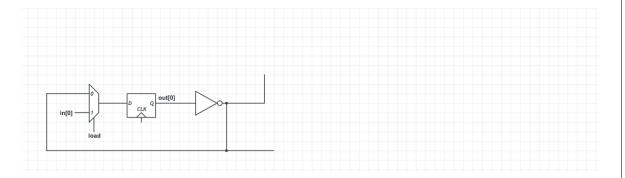

# Problem 3: State of the Machine [16 points, 15 minutes]

Pleased with your work on the charger and battery system from HW1, 151Laptops & Co. has decided to enlist your help once again. You are tasked with building a Mealy-type FSM for managing the laptop's clock frequency depending on load and temperature. The requirements are as follows:

- 1. Input: The FSM has two 1-bit inputs (temperature and load), that are asynchronous to the clock controlling the FSM (clk). These can be concatenated into a 2-bit value {temperature, load} (temperature is the leftmost bit).

- (a) For temperature a value of 1'b0 represents COOL, a value of 1'b1 represents HOT.

- (b) For load a value of 1'b0 represents IDLE, a value of 1'b1 represents BUSY.

| COOL & IDLE | COOL & BUSY | HOT & IDLE | HOT & BUSY |

|-------------|-------------|------------|------------|

| 2'b00       | 2'b01       | 2'b10      | 2'b11      |

2. Output: The FSM has a 2-bit output indicating the frequency that should be used. 2'b00 is the slowest clock and 2'b11 is the fastest clock.

| SLOW  | NORMAL | FAST  | BOOST |

|-------|--------|-------|-------|

| 2'b00 | 2'b01  | 2'b10 | 2'b11 |

- 3. A useful quantity in thinking about this FSM is the **previous output**.

- (a) **Previous output** at any time is defined as the value of the output sampled just before the most recent posedge clk.

- (b) **Previous output** is initially NORMAL.

- 4. In the following scenarios, the output frequency will be dropped to one-level lower than the **previous output**, unless the previous output is already SLOW:

- (a) If the temperature is HOT, or

- (b) If the load is IDLE

- 5. In the following scenario, the output frequency will be increased to one-level higher than the **previous output**, unless the previous output is already BOOST:

- (a) If temperature is COOL and load is BUSY

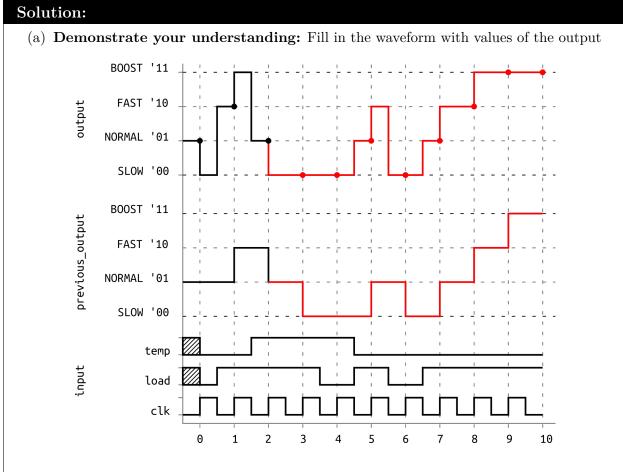

(a) **Demonstrate your understanding:** Fill in the waveform with the values of output and previous output. If you are doing this on a separate paper, it is acceptable to draw only output and previous output so long as you label your axis clearly and mark time.

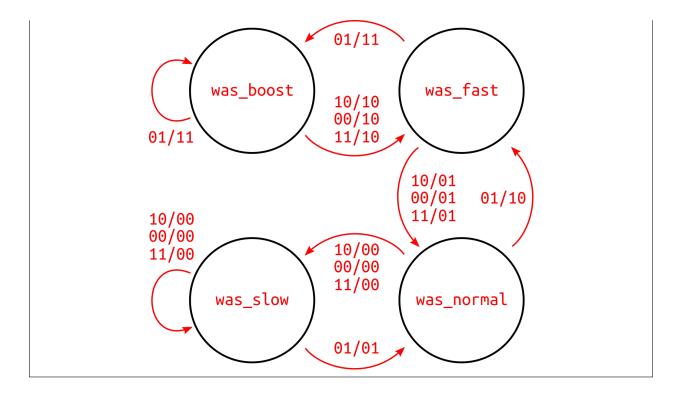

(b) Design it: Draw the state-transition diagram for your Mealy machine. You may use asterisks (\*) to represent "don't care" values: an input of 2'b1\* would indicate temperature=HOT and load is anything.

(b) **Design it:** Draw the state-transition diagram for your mealy machine. You may use asterisks (\*) to represent "don't care": an input of 2'b1\* would indicate temperature=HOT and load is anything.

# Problem 4: Follow the Instructions [18 points, 20 minutes]

You may refer to the RISC-V Green Card on the last pages of this exam.

(a) RISC-V assembly defines a set of standard pseudo-instructions that can be implemented with the base RV32I instructions. Out of the branching pseudo-instructions, select the ones that can be implemented with a single **blt** (branch less than) instruction.

beqz rs, offset (Branch if = 0)

bnez rs, offset (Branch if ≠ 0)

blez rs, offset (Branch if ≤ 0)

bgez rs, offset (Branch if ≥ 0)

bltz rs, offset (Branch if < 0)</li>

bgtz rs, offset (Branch if > 0)

bgt rs, rt, offset (Branch if rs > rt)

ble rs, rt, offset (Branch if rs > rt)

bgtu rs, rt, offset (Branch if rs > rt, unsigned)

bleu rs, rt, offset (Branch if rs ≤ rt, unsigned)

#### Solution:

bltz, bgtz, and bgt

- (b) JALR (jump and link register) uses 12 bits of the immediate, meaning we can only jump to an offset of within 2<sup>11</sup> or 2KiB from the base address. Give the combination of 2 instructions that would allow us to jump to:

- (i) A "PC-absolute" address, i.e. a PC address specified by an absolute 32-bit constant

- (ii) A "PC-relative" address, i.e. a PC address specified by a 32-bit offset from the current PC

| <b>C</b> . | . •     |

|------------|---------|

| 50         | lution: |

| DU.        | iuuuuu  |

| (i)  | LUI + JALR   |

|------|--------------|

| (ii) | AUIPC + JALR |

(c) Notice how imm[0] is discarded (always 0) in B-type instructions. Select all statements below that are TRUE for this ISA design choice.

This explains the difference between S-type and B-type instruction formats.

- An ISA extension with only 16 integer registers prohibits also discarding imm[1].

- An ISA extension with 16-bit instructions prohibits also discarding imm[1].

#### Solution:

Choices #1 and #4

#2: bytes, not instructions

#3: doesn't change instruction length of 32 bits (4 byte increments could allow for lower 2 bits to be discarded)

(d) Based on (c), the JALR instruction could theoretically also discard imm[0]. Select all statements below that would be TRUE if a modified JALR also discarded imm[0].

imm[12] would become redundant based on part (b).

This modified JALR could be encoded as a B-type instruction.

The jump target address range would be expanded by  $2 \times$  without being invalid.

The jump target address of this modified JALR alone would have the same range as regular JAL, which also discards imm[0].

#### Solution:

Choices #1 and #3

#2 would have useless rs2 field that takes away <code>imm</code> bits

#4 cannot because JAL has much larger range (J-type inst.)

(e) Below is the encoding of the "C" (compressed, 16-bit instruction) RISC-V extension. Select all statements below that are TRUE based on the encoding of the fields across the formats.

| Format               | Meaning              | $15 \ 14 \ 13$ | 12         | 11 1         | 09    | 8      | 7  | 6     | 5 | 4   | 3    | <b>2</b> | 1  | 0 |

|----------------------|----------------------|----------------|------------|--------------|-------|--------|----|-------|---|-----|------|----------|----|---|

| $\operatorname{CR}$  | Register             | funct4         |            | rd/rs1       |       | rs2    |    |       |   | op  |      |          |    |   |

| CI                   | Immediate            | funct3         | imm        |              | rd/rs | rd/rs1 |    | ir    |   | mm  |      | op       |    | р |

| $\operatorname{CSS}$ | Stack-relative Store | funct3         | funct3 imm |              | m     | 1      |    |       | r | rs2 |      |          | op |   |

| CIW                  | Wide Immediate       | funct3         | funct3     |              | im    | imm    |    | rd′   |   | rd′ |      | 0        | р  |   |

| CL                   | Load                 | funct3         | unct3 imm  |              |       | rs1'   |    | imm   | 1 |     | rd′  |          | 0  | р |

| CS                   | Store                | funct3 imm     |            | ım           |       | rs1'   |    | imm   | 1 | ]   | rs2' |          | 0  | р |

| CA                   | Arithmetic           | funct6         |            |              | rd    | '/rs   | 1′ | funct | 2 | ]   | rs2' |          | 0  | р |

| CB                   | Branch/Arithmetic    | funct3 offset  |            | set rd'/rs1' |       | offset |    |       | 0 | р   |      |          |    |   |

| CJ                   | Jump                 | funct3         | jump targ  |              | rget  |        |    | op    |   |     |      |          |    |   |

An arithmetic instruction result must overwrite one operand register in the register file.

Only 8 integer registers are available for all compressed instructions.

Jumping to absolute/relative 32-bit addresses is not possible with 2 compressed instructions like in part (b).

Branching instructions (CB format) can only compare against 0, not between 2 registers.

#### Solution:

Choices #1, #3, and #4

#2 is false for CR, CI, and CSS format compressed instructions

# Problem 5: Datapathology [16 points, 15 minutes]

You may refer to the RISC-V Green Card on the last pages of this exam.

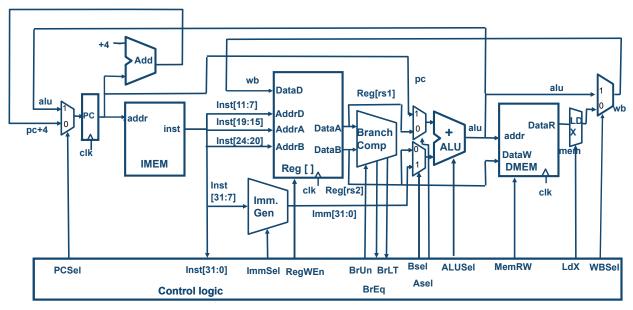

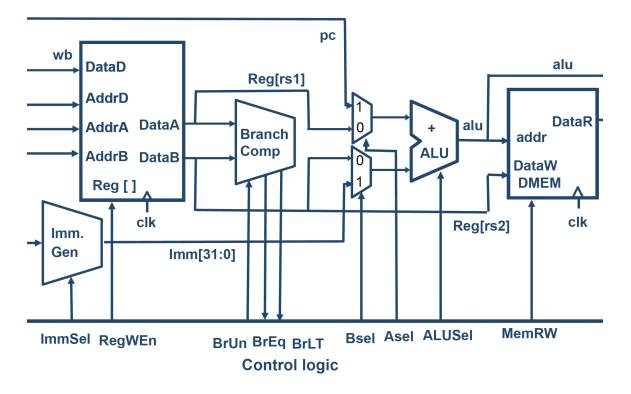

The single-cycle datapath above implements a subset of the RV32I instruction set.

(a) **Datapath functionality:** The Verilog code for an incomplete ALU is given below:

```

wire signed [31:0] in1s, in2s;

assign in1s = in1;

assign in2s = in2;

always Q(*) begin

case (ALUSel)

ADD:

alu = in1 + in2;

SUB:

alu = in1 - in2;

SHIFT_LEFT: alu = in1 << in2[4:0];</pre>

LESS_THAN_S: alu = (in1s < in2s) ? 32'b1 : 32'b0;

SHIFT_RIGHT: alu = in1 >> in2[4:0];

alu = in1 | in2;

OR:

alu = in1 & in2;

AND:

PASS:

alu = in2;

endcase

end

```

Select all instructions below that are supported by the given datapath diagram and the given ALU module:

🗌 LUI rd, imm

AUIPC rd, imm

🗌 BLT rs1, rs2, imm

JALR rd, rs1, imm

LW rd, rs1, imm

SLTU rd, rs1, rs2

SRL rd, rs1, rs2

SRA rd, rs1, rs2

XOR rd, rs1, rs2

AND rd, rs1, rs2

#### Solution:

LUI, AUIPC, BLT, LW, SRL, AND There's no writeback datapath for current address in JALR. SLT is supported but not SLTU. SRL is supported but not SRA. There's no XOR in ALU case.

(b) **New instruction:** In homework 4, we implement ReLU (defined as y = max(0, x)) as an R-type instruction:

relu rd, rs1, rs2

where rs2 is a constant 0 (register x0). We use the branch comparator output to extend the control logic while keeping the ALU in the datapath untouched:

```

// Part of the control logic module

always @(*) begin

ALUSel = ADD; // default

if (opcode == OP || opcode == OP-IMM) begin

// general instructions

end

else if (opcode == CUSTOM-0) begin

ALUSel = BrLT ? AND : OR; // x and 0 = 0, x or 0 = x

end

end

```

Based on this design, now we would like to implement a new R-type instruction, noisy ReLU. Noisy ReLU includes Gaussian noise:  $y = max(0, x + x_{noise})$ . Assume register x1 stores x, register x2 stores  $x_{noise}$ , and we want x3 to have y. noisyrelu x3, x1, x2 is equivalent to the following instructions:

add x4, x1, x2 relu x3, x4, x0 Your Task: How would you modify the datapath to accommodate this instruction? Please draw on the datapath below and label any new control signal you want to use. Try to add as little hardware as possible. Available components (muxes, adders, constants, logic gates) are given below the datapath. Please also explain your design briefly. (If you are doing this on a blank paper, you only need to draw the necessary surroundings so that we can understand you)

Available components:

# Solution:

```

Branch_Comp_input_1 = (NoisyReLU) ? DataA + DataB : DataA;

Branch_Comp_input_2 = (NoisyReLU) ? 32'b0 : DataB;

```

These signals also go to the input of ALU.

- (c) **Timing:** The write ports of **Register File (RF)** and **Data Memory (DMEM)** are synchronized. Your teammate suggests two timing schemes:

- (1) Both writing ports are triggered by the negative edge of clock.

- (2) Both writing ports are triggered by the positive edge of clock.

PC is still updated at the rising edge of clock for both. Will they work properly? Which method do you prefer? Please explain the reason.

#### Solution:

Both work. For (1), IF, ID, EX have to fit in half clock cycle, while (2) can use the full clock cycle. For (2), MA for save instructions and WB actually happen in the next cycle, but asynchronous read can guarantee the correctness. Option (2) can clock faster and is preferred.

Spare page. Will not be graded. Feel free to tear off and use for scratch work.

|                                                                                                                      |                                                                        | GER INSTRUCTIONS, in al                                                                                                                                                                                                    | -                                                                                                                                               | North     |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| MNEMONIC<br>add, addw                                                                                                | FM1<br>R                                                               | NAME<br>ADD (Word)                                                                                                                                                                                                         | DESCRIPTION (in Verilog)<br>R[rd] = R[rs1] + R[rs2]                                                                                             | NOTE<br>1 |

| addi,addiw                                                                                                           | I                                                                      | ADD (word)<br>ADD Immediate (Word)                                                                                                                                                                                         | R[rd] = R[rs1] + R[rs2]<br>R[rd] = R[rs1] + imm                                                                                                 | 1         |

| and                                                                                                                  | R                                                                      | AND                                                                                                                                                                                                                        | R[rd] = R[rs1] & R[rs2]                                                                                                                         | 1         |

| andi                                                                                                                 | ī                                                                      | AND Immediate                                                                                                                                                                                                              | R[rd] = R[rs1] & imm                                                                                                                            |           |

| auipc                                                                                                                | U                                                                      | Add Upper Immediate to PC                                                                                                                                                                                                  | $R[rd] = PC + \{imm, 12'b0\}$                                                                                                                   |           |

| ped                                                                                                                  | SB                                                                     | Branch EQual                                                                                                                                                                                                               | if(R[rs1]==R[rs2)<br>PC=PC+{imm,1b'0}                                                                                                           |           |

| oge                                                                                                                  | SB                                                                     | Branch Greater than or Equal                                                                                                                                                                                               | if(R[rs1]>=R[rs2)<br>PC=PC+{imm,1b'0}                                                                                                           |           |

| ogeu                                                                                                                 | SB                                                                     | $Branch \geq Unsigned$                                                                                                                                                                                                     | if(R[rs1]>=R[rs2)<br>PC=PC+{imm,1b'0}                                                                                                           | 2         |

| olt                                                                                                                  |                                                                        | Branch Less Than                                                                                                                                                                                                           | if(R[rs1] <r[rs2) pc="PC+{imm,1b'0}&lt;/td"><td></td></r[rs2)>                                                                                  |           |

| oltu                                                                                                                 |                                                                        | Branch Less Than Unsigned                                                                                                                                                                                                  | if(R[rs1] <r[rs2) pc="PC+{imm,1b'0}&lt;/td"><td>2</td></r[rs2)>                                                                                 | 2         |

| one                                                                                                                  |                                                                        | Branch Not Equal                                                                                                                                                                                                           | if(R[rs1]!=R[rs2) PC=PC+{imm,1b'0}                                                                                                              |           |

| csrrc                                                                                                                | I                                                                      | Cont./Stat.RegRead&Clear                                                                                                                                                                                                   | $R[rd] = CSR; CSR = CSR \& \sim R[rs1]$                                                                                                         |           |

| csrrci                                                                                                               | Ι                                                                      | Cont./Stat.RegRead&Clear<br>Imm                                                                                                                                                                                            | $R[rd] = CSR;CSR = CSR \& \sim imm$                                                                                                             |           |

| csrrs                                                                                                                | Ι                                                                      | Cont./Stat.RegRead&Set                                                                                                                                                                                                     | R[rd] = CSR; CSR = CSR   R[rs1]                                                                                                                 |           |

| csrrsi                                                                                                               | Ι                                                                      | Cont./Stat.RegRead&Set<br>Imm                                                                                                                                                                                              | $R[rd] = CSR; CSR = CSR \mid imm$                                                                                                               |           |

| csrrw                                                                                                                | Ι                                                                      | Cont./Stat.RegRead&Write                                                                                                                                                                                                   | R[rd] = CSR; CSR = R[rs1]                                                                                                                       |           |

| csrrwi                                                                                                               | Ι                                                                      | Cont./Stat.Reg Read&Write<br>Imm                                                                                                                                                                                           | R[rd] = CSR; CSR = imm                                                                                                                          |           |

| ebreak                                                                                                               | Ι                                                                      | Environment BREAK                                                                                                                                                                                                          | Transfer control to debugger                                                                                                                    |           |

| ecall                                                                                                                | I                                                                      | Environment CALL                                                                                                                                                                                                           | Transfer control to operating system                                                                                                            |           |

| fence                                                                                                                | I                                                                      | Synch thread                                                                                                                                                                                                               | Synchronizes threads                                                                                                                            |           |

| fence.i                                                                                                              | Ι                                                                      | Synch Instr & Data                                                                                                                                                                                                         | Synchronizes writes to instruction stream                                                                                                       |           |

| jal                                                                                                                  | UJ                                                                     | Jump & Link                                                                                                                                                                                                                | $R[rd] = PC+4; PC = PC + \{imm, 1b'0\}$                                                                                                         |           |

| jalr                                                                                                                 | I                                                                      | Jump & Link Register                                                                                                                                                                                                       | R[rd] = PC+4; PC = R[rs1]+imm                                                                                                                   | 3         |

| lb                                                                                                                   | Ι                                                                      | Load Byte                                                                                                                                                                                                                  | R[rd] =<br>{56'bM[](7),M[R[rs1]+imm](7:0)}                                                                                                      | 4         |

| lbu                                                                                                                  | I                                                                      | Load Byte Unsigned                                                                                                                                                                                                         | $R[rd] = {56'b0, M[R[rs1]+imm](7:0)}$                                                                                                           |           |

| ld                                                                                                                   | I                                                                      | Load Doubleword                                                                                                                                                                                                            | R[rd] = M[R[rs1]+imm](63:0)                                                                                                                     |           |

| lh                                                                                                                   | Ι                                                                      | Load Halfword                                                                                                                                                                                                              | R[rd] =<br>{48'bM[](15),M[R[rs1]+imm](15:0)}                                                                                                    | 4         |

| lhu                                                                                                                  | I                                                                      | Load Halfword Unsigned                                                                                                                                                                                                     | $R[rd] = \{48'b0, M[R[rs1]+imm](15:0)\}$                                                                                                        |           |

| lui                                                                                                                  | Ū                                                                      | Load Upper Immediate                                                                                                                                                                                                       | $R[rd] = \{32b'imm<31>, imm, 12'b0\}$                                                                                                           |           |

| lw                                                                                                                   | Ι                                                                      | Load Word                                                                                                                                                                                                                  | R[rd] =<br>{32'bM[](31),M[R[rs1]+imm](31:0)}                                                                                                    | 4         |

| lwu                                                                                                                  | I                                                                      | Load Word Unsigned                                                                                                                                                                                                         | $R[rd] = {32'b0, M[R[rs1]+imm](31:0)}$                                                                                                          |           |

| or                                                                                                                   | R                                                                      | OR                                                                                                                                                                                                                         | R[rd] = R[rs1]   R[rs2]                                                                                                                         |           |

| ori                                                                                                                  | Ι                                                                      | OR Immediate                                                                                                                                                                                                               | $R[rd] = R[rs1] \mid imm$                                                                                                                       |           |

| sb                                                                                                                   | S                                                                      | Store Byte                                                                                                                                                                                                                 | M[R[rs1]+imm](7:0) = R[rs2](7:0)                                                                                                                |           |

| sd                                                                                                                   | S                                                                      | Store Doubleword                                                                                                                                                                                                           | M[R[rs1]+imm](63:0) = R[rs2](63:0)                                                                                                              |           |

| sh                                                                                                                   | S                                                                      | Store Halfword                                                                                                                                                                                                             | M[R[rs1]+imm](15:0) = R[rs2](15:0)                                                                                                              |           |

| sll,sllw                                                                                                             | R                                                                      | Shift Left (Word)                                                                                                                                                                                                          | $R[rd] = R[rs1] \iff R[rs2]$                                                                                                                    | 1         |

| slli,slliw<br>slt                                                                                                    | I<br>R                                                                 | Shift Left Immediate (Word)                                                                                                                                                                                                | $R[rd] = R[rs1] \ll imm$                                                                                                                        | 1         |

| siti                                                                                                                 | к<br>I                                                                 | Set Less Than<br>Set Less Than Immediate                                                                                                                                                                                   | R[rd] = (R[rs1] < R[rs2]) ? 1 : 0<br>R[rd] = (R[rs1] < imm) ? 1 : 0                                                                             |           |

| sltiu                                                                                                                | I                                                                      | Set < Immediate Unsigned                                                                                                                                                                                                   | R[rd] = (R[rs1] < imm) ? 1 : 0                                                                                                                  | 2         |

| sltu                                                                                                                 | R                                                                      | Set Less Than Unsigned                                                                                                                                                                                                     | R[rd] = (R[rs1] < R[rs2]) ? 1 : 0                                                                                                               | 2         |

| sra,sraw                                                                                                             | R                                                                      | Shift Right Arithmetic (Word)                                                                                                                                                                                              |                                                                                                                                                 | 1,5       |

| srai,sraiw                                                                                                           | Ι                                                                      | Shift Right Arith Imm (Word)                                                                                                                                                                                               | R[rd] = R[rs1] >> imm                                                                                                                           | 1,5       |

| srl,srlw                                                                                                             | R                                                                      | Shift Right (Word)                                                                                                                                                                                                         | $R[rd] = R[rs1] \gg R[rs2]$                                                                                                                     | 1         |

| srli,srliw                                                                                                           | Ι                                                                      | Shift Right Immediate (Word)                                                                                                                                                                                               | R[rd] = R[rs1] >> imm                                                                                                                           | 1         |

| sub,subw                                                                                                             | R                                                                      | SUBtract (Word)                                                                                                                                                                                                            | R[rd] = R[rs1] - R[rs2]                                                                                                                         | 1         |

| ΒW                                                                                                                   | S                                                                      | Store Word                                                                                                                                                                                                                 | M[R[rs1]+imm](31:0) = R[rs2](31:0)                                                                                                              |           |

| kor                                                                                                                  | R                                                                      | XOR                                                                                                                                                                                                                        | $R[rd] = R[rs1] \land R[rs2]$                                                                                                                   |           |

| kori<br>Notes: 1) The                                                                                                | I<br>Word                                                              | XOR Immediate                                                                                                                                                                                                              | $R[rd] = R[rs1] \land imm$<br>ightmost 32 bits of a 64-bit registers                                                                            |           |

| <ol> <li>2) Ope</li> <li>3) The</li> <li>4) (sign</li> <li>5) Repu</li> <li>6) Mul.</li> <li>7) The bit H</li> </ol> | ration<br>least :<br>ned) L<br>licates<br>tiply v<br>Single<br>7 regis | a assumes unsigned integers (in<br>significant bit of the branch ad<br>oad instructions extend the sig<br>the sign bit to fill in the leftma<br>with one operand signed and or<br>e version does a single-precisio<br>ster | stead of 2's complement)<br>dress in jalr is set to 0<br>n bit of data to fill the 64-bit register<br>ost bits of the result during right shift |           |

| RV64M Multiply Exten                       | sion     |                                  |                                                                                                                              |    |

|--------------------------------------------|----------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------|----|

| MNEMONIC                                   |          | NAME                             | DESCRIPTION (in Verilog)                                                                                                     | NO |

| mul, mulw                                  | R        | MULtiply (Word)                  | R[rd] = (R[rs1] * R[rs2])(63:0)                                                                                              |    |

| mulh                                       | R        | MULtiply High                    | R[rd] = (R[rs1] * R[rs2])(127:64)                                                                                            |    |

| mulhu                                      | R        | MULtiply High Unsigned           | R[rd] = (R[rs1] * R[rs2])(127:64)                                                                                            |    |

| mulhsu                                     | R        |                                  | R[rd] = (R[rs1] * R[rs2])(127:64)                                                                                            |    |

| div,divw                                   | R        | DIVide (Word)                    | R[rd] = (R[rs1] / R[rs2])                                                                                                    |    |

| divu                                       | R        | DIVide Unsigned                  | R[rd] = (R[rs1] / R[rs2])                                                                                                    |    |

| rem, remw                                  | R        | REMainder (Word)                 | R[rd] = (R[rs1] % R[rs2])                                                                                                    |    |

| remu, remuw                                | R        | REMainder Unsigned<br>(Word)     | R[rd] = (R[rs1] % R[rs2])                                                                                                    |    |

| RV64F and RV64D Flo                        |          |                                  |                                                                                                                              |    |

| fld,flw                                    | Ι        | Load (Word)                      | F[rd] = M[R[rs1]+imm]                                                                                                        |    |

| fsd,fsw                                    | S        | Store (Word)                     | M[R[rs1]+imm] = F[rd]                                                                                                        |    |

| fadd.s,fadd.d                              | R        | ADD                              | F[rd] = F[rs1] + F[rs2]                                                                                                      |    |

| fsub.s,fsub.d                              | R        | SUBtract                         | F[rd] = F[rs1] - F[rs2]                                                                                                      |    |

| fmul.s,fmul.d                              | R        | MULtiply<br>DIVide               | F[rd] = F[rs1] * F[rs2]                                                                                                      |    |

| fdiv.s,fdiv.d                              | R        |                                  | $\mathbf{F}[\mathbf{rd}] = \mathbf{F}[\mathbf{rs1}] / \mathbf{F}[\mathbf{rs2}]$                                              |    |

| fsqrt.s,fsqrt.d                            | R        | SQuare RooT                      | F[rd] = sqrt(F[rs1])                                                                                                         |    |

| fmadd.s,fmadd.d                            | R        | Multiply-ADD                     | F[rd] = F[rs1] * F[rs2] + F[rs3]                                                                                             |    |

| fmsub.s,fmsub.d                            | R        | Multiply-SUBtract                | F[rd] = F[rs1] * F[rs2] - F[rs3]                                                                                             |    |

| fnmadd.s,fnmadd.d<br>fnmsub.s,fnmsub.d     | R<br>R   | Negative Multiply-ADD            | F[rd] = -(F[rs1] * F[rs2] + F[rs3])<br>F[rd] = -(F[rs1] * F[rs2] - F[rs3])                                                   |    |

| fsgnj.s,fsgnj.d                            | R        | SiGN source                      | $F[rd] = \{F[rs2] < 63 >, F[rs1] < 62:0 >\}$                                                                                 |    |

| fsgnjn.s,fsgnjn.d                          | R        | Negative SiGN source             | $F[rd] = \{ (\sim F[rs2] < 63>), F[rs1] < 62:0> \}$                                                                          |    |

| fsgnjx.s,fsgnjx.d                          | R        | Xor SiGN source                  | $F[rd] = \{F[rs2] < 63 > , F[rs1] < 63 >, F[rs1] < 63 >, F[rs1] < 62 : 0 > \}$                                               |    |

| fmin.s,fmin.d                              | R        | MINimum                          | F[rd] = (F[rs1] < F[rs2]) ? F[rs1] : F[rs2]                                                                                  |    |

| fmax.s, fmax.d                             | R        | MAXimum                          | F[rd] = (F[rs1] > F[rs2]) ? F[rs1] : F[rs2]                                                                                  |    |

| feq.s, feq.d                               | R        | Compare Float EQual              | R[rd] = (F[rs1] = F[rs2]) ? 1 : 0                                                                                            |    |

| flt.s,flt.d                                | R        | Compare Float Less Than          | R[rd] = (F[rs1] < F[rs2]) ? 1 : 0                                                                                            |    |

| fle.s,fle.d                                | R        | Compare Float Less than or =     | $R[rd] = (F[rs1] \le F[rs2]) ? 1 : 0$                                                                                        |    |

| fclass.s,fclass.d                          | R        | Classify Type                    | R[rd] = class(F[rs1])                                                                                                        |    |

| fmv.s.x,fmv.d.x                            | R        | Move from Integer                | F[rd] = R[rs1]                                                                                                               |    |

| fmv.x.s,fmv.x.d                            | R        | Move to Integer                  | R[rd] = F[rs1]                                                                                                               |    |

| fcvt.s.d                                   | R        | Convert to SP from DP            | F[rd] = single(F[rs1])                                                                                                       |    |

| fcvt.d.s                                   | R        | Convert to DP from SP            | F[rd] = double(F[rs1])                                                                                                       |    |

| fcvt.s.w,fcvt.d.w                          | R        | Convert from 32b Integer         | F[rd] = float(R[rs1](31:0))                                                                                                  |    |

| fcvt.s.l,fcvt.d.l                          | R        | Convert from 64b Integer         | F[rd] = float(R[rs1](63:0))                                                                                                  |    |

| fcvt.s.wu,fcvt.d.wu                        |          | Convert from 32b Int<br>Unsigned | F[rd] = float(R[rs1](31:0))                                                                                                  |    |

| fcvt.s.lu,fcvt.d.lu                        |          | Convert from 64b Int<br>Unsigned | F[rd] = float(R[rs1](63:0))                                                                                                  |    |

| fcvt.w.s,fcvt.w.d                          | R        | Convert to 32b Integer           | R[rd](31:0) = integer(F[rs1])                                                                                                |    |

| fcvt.l.s,fcvt.l.d                          | R        | Convert to 64b Integer           | R[rd](63:0) = integer(F[rs1])                                                                                                |    |

| fcvt.wu.s,fcvt.wu.d                        |          |                                  | R[rd](31:0) = integer(F[rs1])                                                                                                |    |

| fcvt.lu.s,fcvt.lu.d                        |          | Convert to 64b Int Unsigned      | R[rd](63:0) = integer(F[rs1])                                                                                                |    |

| RV64A Atomtic Extens<br>amoadd.w, amoadd.d | ion<br>R | ADD                              | R[rd] = M[R[rs1]],<br>M[P[rs11] = M[P[rs11] + P[rs2]]                                                                        |    |

| amoand.w,amoand.d                          | R        | AND                              | M[R[rs1]] = M[R[rs1]] + R[rs2]<br>R[rd] = M[R[rs1]],<br>M[R[rs1]] = M[R[rs1]] & R[rs2]                                       |    |

| amomax.w,amomax.d                          | R        | MAXimum                          | R[rd] = M[R[rs1]],<br>if $(R[rs2] > M[R[rs1]]) M[R[rs1]] = R[rs2]$                                                           |    |

| amomaxu.w,amomaxu.d                        | R        | MAXimum Unsigned                 | R[rd] = M[R[rs1]],<br>if (R[rs2] > M[R[rs1]]) M[R[rs1]] = R[rs2]                                                             |    |

| amomin.w,amomin.d                          | R        | MINimum                          | R[rd] = M[R[rs1]],<br>if (R[rs2] < M[R[rs1]]) M[R[rs1]] = R[rs2]                                                             |    |

| amominu.w,amominu.d                        | R        | MINimum Unsigned                 | R[rd] = M[R[rs1]],<br>if $(R[rs2] < M[R[rs1]]) M[R[rs1]] = R[rs2]$                                                           |    |

| amoor.w,amoor.d                            | R        | OR                               | R[rd] = M[R[rs1]],<br>M[R[rs1]] = M[R[rs1]]   R[rs2]                                                                         |    |

| amoswap.w,amoswap.d<br>amoxor.w,amoxor.d   | R<br>R   | SWAP<br>XOR                      | $\begin{split} R[rd] &= M[R[rs1]], M[R[rs1]] = R[rs2] \\ R[rd] &= M[R[rs1]], \\ M[R[rs1]] &= M[R[rs1]] ^ R[rs2] \end{split}$ |    |

| lr.w,lr.d                                  | R        | Load Reserved                    | R[rd] = M[R[rs1]],<br>reservation on M[R[rs1]]                                                                               |    |

|                                            |          |                                  |                                                                                                                              |    |

۲

#### CORE INSTRUCTION FORMATS

|    | 31                    | 27 | 26 | 25 | 24         | 20  | 19 | 15         | 14  | 12       | 11     | 7      | 6    | 0   |

|----|-----------------------|----|----|----|------------|-----|----|------------|-----|----------|--------|--------|------|-----|

| R  | funct7                |    |    | r  | s2         | rsl |    | funct3     |     | rd       |        | Opcode |      |     |

| I  | imm[11:0]             |    |    | r  | rs1 funct3 |     |    | rd         |     | Opcode   |        |        |      |     |

| s  | imm[11:5]             |    |    | rs | s2         | rsl |    | rs1 funct3 |     | imm[4:0] |        | opeo   | ode  |     |

| SB | imm[12 10:5] rs2      |    |    |    |            | r   | 51 | fun        | ct3 | imm[4    | :1 11] | opco   | ode  |     |

| U  | imm[31:12]            |    |    |    |            |     |    |            |     |          | ro     | i      | opco | ode |

| UJ | imm[20 10:1 11 19:12] |    |    |    |            |     |    |            |     |          | ro     | ł      | opeo | ode |

© 2018 by Elsevier, Inc. All rights reserved. From Patterson and Hennessy, Computer Organization and Design: The Hardware/Software Interface: RISC-V Edition

۲

I

۲

#### PSEUDO INSTRUCTIONS

۲

| MNEMONIC      | NAME           | DESCRIPTION                              | USES   |

|---------------|----------------|------------------------------------------|--------|

| beqz          | Branch = zero  | if(R[rs1]==0) PC=PC+{imm,1b'0}           | beq    |

| bnez          | Branch ≠ zero  | if(R[rs1]!=0) PC=PC+{imm,1b'0}           | bne    |

| fabs.s,fabs.d | Absolute Value | F[rd] = (F[rs1] < 0) ? - F[rs1] : F[rs1] | fsgnx  |

| fmv.s,fmv.d   | FP Move        | F[rd] = F[rs1]                           | fsgnj  |

| fneg.s,fneg.d | FP negate      | F[rd] = -F[rs1]                          | fsgnjn |

| j             | Jump           | $PC = \{imm, 1b'0\}$                     | jal    |

| jr            | Jump register  | PC = R[rs1]                              | jalr   |

| la            | Load address   | R[rd] = address                          | auipc  |

| 1i            | Load imm       | R[rd] = imm                              | addi   |

| mv            | Move           | R[rd] = R[rs1]                           | addi   |

| neg           | Negate         | R[rd] = -R[rs1]                          | sub    |

| nop           | No operation   | R[0] = R[0]                              | addi   |

| not           | Not            | $R[rd] = \sim R[rs1]$                    | xori   |

| ret           | Return         | PC = R[1]                                | jalr   |

| seqz          | Set = zero     | R[rd] = (R[rs1] == 0) ? 1 : 0            | sltiu  |

| snez          | Set ≠ zero     | R[rd] = (R[rs1]!= 0) ? 1 : 0             | sltu   |

|               |                |                                          |        |

# OPCODES IN NUMERICAL ORDER BY OPCODE MNEMONIC FMT OPCODE FUNCT3 FUNCT7 OR IMM HEXADECIMA

| MNEMONIC   | FMT    | OPCODE             | FUNCT3 | FUNCT7 OR IMN | A HEXADECIMA       |

|------------|--------|--------------------|--------|---------------|--------------------|

| lb         | I      | 0000011            | 000    |               | 03/0               |

| lh         | I      | 0000011            | 001    |               | 03/1               |

| lw         | Ι      | 0000011            | 010    |               | 03/2               |

| ld         | I      | 0000011            | 011    |               | 03/3               |

| lbu        | Ι      | 0000011            | 100    |               | 03/4               |

| lhu        | Ι      | 0000011            | 101    |               | 03/5               |

| lwu        | I      | 0000011            | 110    |               | 03/6               |

| fence      | Ι      | 0001111            | 000    |               | OF/O               |

| fence.i    | Ι      | 0001111            | 001    |               | 0F/1               |

| addi       | I      | 0010011            | 000    |               | 13/0               |

| slli       | Ι      | 0010011            | 001    | 0000000       | 13/1/00            |

| slti       | Ι      | 0010011            | 010    |               | 13/2               |

| sltiu      | I      | 0010011            | 011    |               | 13/3               |

| xori       | I      | 0010011            | 100    |               | 13/4               |

| srli       | I      | 0010011            | 101    | 0000000       | 13/5/00            |

| srai       | I      | 0010011            | 101    | 0100000       | 13/5/20            |

| ori        | I      | 0010011            | 110    |               | 13/6               |

| andi       | I      | 0010011            | 111    |               | 13/7               |

| auipc      | U      | 0010111            | 000    |               | 17                 |

| addiw      | I      | 0011011            | 000    |               | 1B/0               |

| slliw      | I      | 0011011            | 001    | 0000000       | 1B/1/00            |

| srliw      | I      | 0011011            | 101    | 0000000       | 1B/5/00            |

| sraiw      | I      | 0011011            | 101    | 0100000       | 1B/5/20            |

| sb         | S      | 0100011            | 000    |               | 23/0               |

| sh         | S      | 0100011            | 001    |               | 23/1               |

| SW         | S      | 0100011            | 010    |               | 23/2               |

| sd<br>add  | S      | 0100011<br>0110011 | 011    | 0000000       | 23/3<br>33/0/00    |

|            | R      |                    |        | 0100000       |                    |

| sub<br>sll | R      | 0110011<br>0110011 | 000    | 0000000       | 33/0/20<br>33/1/00 |

| slt        | R      | 0110011            | 010    | 0000000       | 33/2/00            |

| situ       | R      | 0110011            | 010    | 0000000       | 33/3/00            |

| xor        | R      | 0110011            | 100    | 0000000       | 33/4/00            |

| srl        | R<br>R | 0110011            | 101    | 0000000       | 33/5/00            |

| sra        | R      | 0110011            | 101    | 0100000       | 33/5/20            |

| or         | R      | 0110011            | 110    | 0000000       | 33/6/00            |

| and        | R      | 0110011            | 111    | 0000000       | 33/7/00            |

| lui        | U      | 01100111           | 111    | 0000000       | 37                 |

| addw       | R      | 0111011            | 000    | 0000000       | 3B/0/00            |

| subw       | R      | 0111011            | 000    | 0100000       | 3B/0/20            |

| sllw       | R      | 0111011            | 001    | 0000000       | 3B/1/00            |

| srlw       | R      | 0111011            | 101    | 0000000       | 3B/5/00            |

| sraw       | R      | 0111011            | 101    | 0100000       | 3B/5/20            |

| beq        | SB     | 1100011            | 000    | 0100000       | 63/0               |

| bne        | SB     | 1100011            | 001    |               | 63/1               |

| blt        | SB     | 1100011            | 100    |               | 63/4               |

| bge        | SB     | 1100011            | 101    |               | 63/5               |

| bltu       | SB     | 1100011            | 110    |               | 63/6               |

| bgeu       | SB     | 1100011            | 111    |               | 63/7               |

| jalr       | I      | 1100111            | 000    |               | 67/0               |

| jal        | ŵ      | 1101111            |        |               | 6F                 |

| ecall      | I      | 1110011            | 000    | 0000000000000 | 73/0/000           |

| ebreak     | Î      | 1110011            | 000    | 000000000001  | 73/0/001           |

| CSRRW      | î      | 1110011            | 001    |               | 73/1               |

| CSRRS      | î      | 1110011            | 010    |               | 73/2               |

| CSRRC      | Î      | 1110011            | 011    |               | 73/3               |

| CSRRWI     | î      | 1110011            | 101    |               | 73/5               |

| CSRRSI     | î      | 1110011            | 110    |               | 73/6               |

| CSRRCI     | Î      | 1110011            | 111    |               | 73/7               |

|            | -      |                    |        |               |                    |

#### 3 REGISTER NAME, USE, CALLING CONVENTION

| GISTER NAM | E, USE, CALLIN | G CONVENTION                        | 4     |

|------------|----------------|-------------------------------------|-------|

| REGISTER   | NAME           | USE                                 | SAVE  |

| x0         | zero           | The constant value 0                | N.A.  |

| xl         | ra             | Return address                      | Calle |

| x2         | sp             | Stack pointer                       | Calle |

| x3         | gp             | Global pointer                      |       |

| x4         | tp             | Thread pointer                      |       |

| x5-x7      | t0-t2          | Temporaries                         | Calle |

| x8         | s0/fp          | Saved register/Frame pointer        | Calle |

| x9         | s1             | Saved register                      | Calle |

| x10-x11    | a0-a1          | Function arguments/Return values    | Calle |

| x12-x17    | a2-a7          | Function arguments                  | Calle |

| x18-x27    | s2-s11         | Saved registers                     | Calle |

| x28-x31    | t3-t6          | Temporaries                         | Calle |

| f0-f7      | ft0-ft7        | FP Temporaries                      | Calle |

| f8-f9      | fs0-fs1        | FP Saved registers                  | Calle |

| f10-f11    | fa0-fa1        | FP Function arguments/Return values | Calle |

| f12-f17    | fa2-fa7        | FP Function arguments               | Calle |

| f18-f27    | fs2-fs11       | FP Saved registers                  | Calle |

| f28-f31    | ft8-ft11       | R[rd] = R[rs1] + R[rs2]             | Calle |

#### IEEE 754 FLOATING-POINT STANDARD

| SIZE             | PREFIX | SYMBOL | SIZE              | PREFIX | SYMBOL |

|------------------|--------|--------|-------------------|--------|--------|

| $10^{3}$         | Kilo-  | K      | 210               | Kibi-  | Ki     |

| $10^{6}$         | Mega-  | M      | $2^{20}$          | Mebi-  | Mi     |

| 109              | Giga-  | G      | 2 <sup>30</sup>   | Gibi-  | Gi     |

| $10^{12}$        | Tera-  | Т      | $2^{40}$          | Tebi-  | Ti     |

| 10 <sup>15</sup> | Peta-  | Р      | 2 <sup>50</sup>   | Pebi-  | Pi     |

| 1018             | Exa-   | E      | $2^{60}$          | Exbi-  | Ei     |

| $10^{21}$        | Zetta- | Z      | 270               | Zebi-  | Zi     |

| $10^{24}$        | Yotta- | Y      | 2 <sup>80</sup>   | Yobi-  | Yi     |

| 10-3             | milli- | m      | 10-15             | femto- | f      |

| 10-6             | micro- | μ      | 10 <sup>-18</sup> | atto-  | a      |

| 10.9             | nano-  | n      | 10 <sup>-21</sup> | zepto- | z      |

| 10-12            | pico-  | р      | 10 <sup>-24</sup> | yocto- | y      |

| © 2018 by Elsevier. Inc. All rights reserved. | From Patterson and Hennessy. ( | Computer Organization and Design | The Hardware/Software Interface: RISC-V Edition |

|-----------------------------------------------|--------------------------------|----------------------------------|-------------------------------------------------|

|                                               |                                |                                  |                                                 |

# Fold bottom side (columns 3 and 4) together l ri 1. Pull along perforation to separate card L

۲

L Т Т L

L

L

I L I L I I

I

I

L

L

L

L

I

I

I

I

I

I I

Т L

> L I.

| 31                    | 27         | 26   | 25   | 24 |     | 20 | 19           | 15 | 14   | 12     | 11     | 7        | 6  | 0    |        |

|-----------------------|------------|------|------|----|-----|----|--------------|----|------|--------|--------|----------|----|------|--------|

|                       | funct7     |      |      |    | rs2 |    | $\mathbf{r}$ | s1 | fun  | ct3    |        | rd       | op | code | R-type |

|                       | ir         | nm[  | 11:0 | )] |     |    | $\mathbf{r}$ | s1 | fun  | ct3    |        | rd       | op | code | I-type |

|                       | imm[11:    | 5]   |      |    | rs2 |    | rs           | s1 | fun  | ct3    | imr    | n[4:0]   | op | code | S-type |

| in                    | nm[12 10]  | ):5] |      |    | rs2 |    | rs           | s1 | fun  | ct3    | imm    | [4:1 11] | op | code | B-type |

|                       | imm[31:12] |      |      |    |     |    |              | rd | op   | code   | U-type |          |    |      |        |

| imm[20 10:1 11 19:12] |            |      |      |    |     |    | rd           | op | code | J-type |        |          |    |      |        |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                |              | RV32I | Base Instru | uction S | et          |         |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-------------|----------|-------------|---------|--------|

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                |              |       |             | rd       |             |         |        |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                |              |       |             |          | rd          |         | AUIPC  |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                |              |       | 9:12]       |          | rd          | 1101111 |        |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                | imm[11:      | 0]    | rs1         | 000      | rd          | 1100111 | JALR   |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                | imm[12 10:5] | rs2   | rs1         | 000      | imm[4:1 11] | 1100011 | BEQ    |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                |              | rs2   | rs1         | 001      | imm[4:1 11] | 1100011 |        |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                | imm[12 10:5] |       | rs1         | 100      |             | 1100011 |        |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                | imm[12 10:5] |       | rs1         | 101      |             | 1100011 | BGE    |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                |              | rs2   | rs1         | 110      | imm[4:1 11] | 1100011 | BLTU   |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                | imm[12 10:5] | rs2   | rs1         | 111      | imm[4:1 11] | 1100011 | BGEU   |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                | imm[11:      | 0]    | rs1         | 000      | rd          | 0000011 |        |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                |              |       | rs1         | 001      | rd          | 0000011 |        |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                | imm[11:      | 0]    | rs1         | 010      | rd          | 0000011 | ] LW   |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                |              |       | rs1         | 100      | rd          | 0000011 | ] LBU  |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                | imm[11:      | 0]    | rs1         | 101      | rd          | 0000011 |        |