UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences

Professor Oldham

Fall 1999

# EECS 40 — MIDTERM #2

10 November 1999

Name: \_\_\_\_\_

Last, First

Student ID: \_\_\_\_\_

TA: □ Kusuma □ Chang

### **Guidelines:**

- 1. Closed book and notes except 1 page of formulas.

- **2.** You may use a calculator.

- **3.** Do not unstaple the exam.

- 4. Show all your work and reasoning on the exam in order to receive full or partial credit.

- 5. This exam contains 12 pages plus the cover page and 2 sheets of scratch paper included at the end of the exam. You can remove these from the rest of the exam if you wish.

| Problem | Points<br>Possible | Your<br>Score |

|---------|--------------------|---------------|

| 1       | 20                 |               |

| 2       | 20                 |               |

| 3       | 20                 |               |

| 4       | 20                 |               |

| 5       | 20                 |               |

| Total   | 100                |               |

|   |   | 10 <sup>3</sup> |

|---|---|-----------------|

| m | = | $10^{-3}$       |

| μ | = | 10-6            |

|   |   | $10^{-9}$       |

| р | = | $10^{-12}$      |

| f | = | $10^{-15}$      |

|   |   |                 |

#### Problem 1 (20 points)

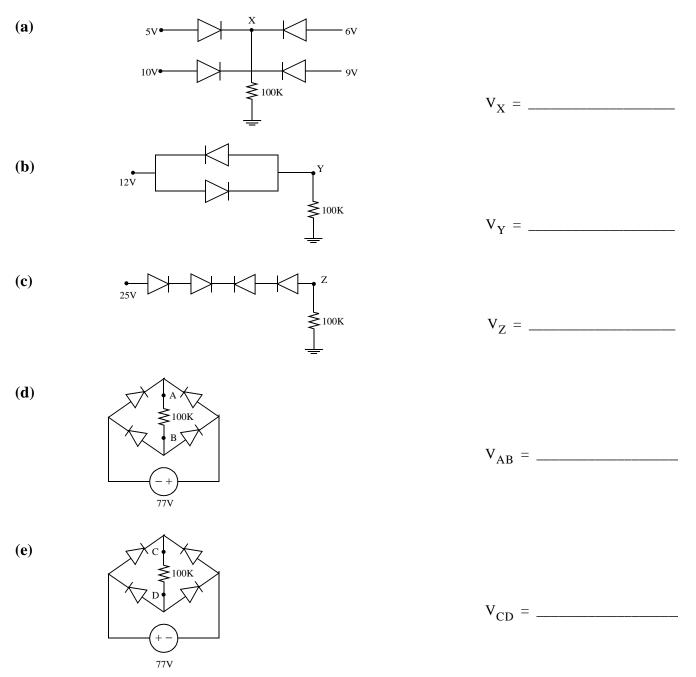

What is the value of the unknown node voltage in each of the following circuits? Assume diodes are perfect rectifiers.

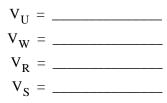

(f) A cross-section for a CMOS chip is shown on the facing page. Some node voltages are indicated. Please tell us what the values are for the node voltages at nodes U, W, R, S.

Prob. 1 Worksheet

#### Problem 2 (20 points)

Shown on the opposite page is the layout and two cross-sections through a CMOS inverter. A list of components follows. You are to indicate, by labelling, the location of that feature on the figure. The first question is used as an example.

## 2.1 Layout

- (1) A contact to polysilicon [EXAMPLE]

- (2) gate of NMOS transistor

- (3) the W dimension of the PMOS transistor

- (4) contact to p-type substrate

- (5) metal contact to PMOS gate

- (6) spacing from n+ source gain areas to well mask

- (7) input electrode

- (8) output electrode

## 2.2 Cross-sections

- (a) well region

- (b) field oxide

- (c) NMOS gate oxide

- (d) metal contact to PMOS source or drain

- (e) poly on field oxide

- (f) metal over field oxide

- (g) contact to NMOS source or drain

- (h) oxide over polysilicon gate

## 2.3 Masks

A possible list of masks for this process follows. You are to order the masks by simply filling in the mask number. It is possible that one or more masks is missing. If so, you must fill out a new mask row for each missing mask.

|                | MASK#    | NAME     | FUNCTION                       |

|----------------|----------|----------|--------------------------------|

|                |          | Poly     | Define polysilicon areas       |

|                |          | N-select | Define n+ implant areas        |

|                |          | P-select | Define p+ implant areas        |

|                |          | Oxide    | Define areas for gate oxide    |

|                |          | Metal    | Define metal conductor pattern |

|                |          |          |                                |

| Fill in mask # |          |          |                                |

| here           | <b>A</b> |          |                                |

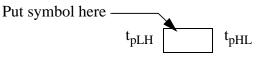

### 2.4 Gate delay

For this layout, what do we expect for the relationship between gate delay for output rising ( $t_{pLH}$ ), and output falling ( $t_{pHL}$ )? Answer by putting in the correct symbol in the box (=, >, or <).

Why? \_\_\_\_\_

## **Prob. 2 – Schematic for CMOS Inverter**

#### Problem 3 (20 points)

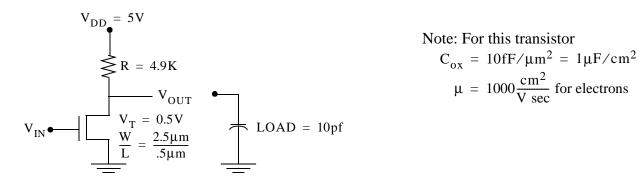

You are trying to construct a dc switch with an MOS transistor, as shown below. The idea: When input is low, output high. But when input is high, output is hopefully low.

(a) If  $V_{IN} = 5V$ , what is the channel electron charge (coulomb/cm<sup>2</sup>)(for small values of  $V_{OUT}$  only)?

formula \_\_\_\_\_

value \_\_\_\_\_

(b) If  $V_{IN} = 5 V$ , what is the sheet resistance of the channel? (Again for the case in which  $V_{OUT}$  is very small.)

formula \_\_\_\_\_

value \_\_\_\_\_

(c) What is the value of  $V_{IN}$  needed to produce an output of 0.1 V?

V<sub>IN</sub> = \_\_\_\_\_

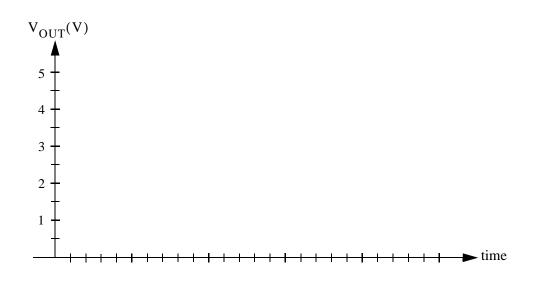

(d) If the input suddenly switches low, and the load is 10 pF, as shown, sketch the output voltage versus time (accurately) and estimate the time  $\Delta t$  for the output to go from 0.1 V to 2.45V (halfway to 5 V).

$\Delta t = \____n sec$

**(d)**

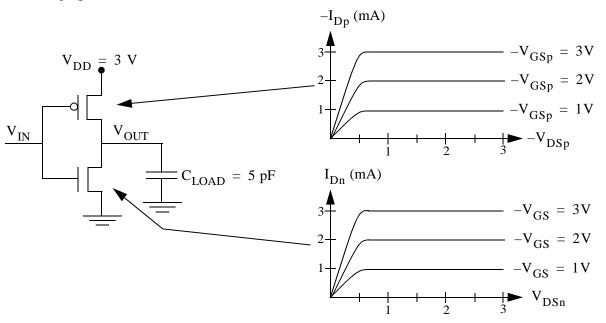

#### Problem 4 (20 points)

A CMOS inverter drives an off-chip capacitance load, as shown below. All you know about the MOS transistors is shown in the graphs. (DO NOT ASK for more information!)

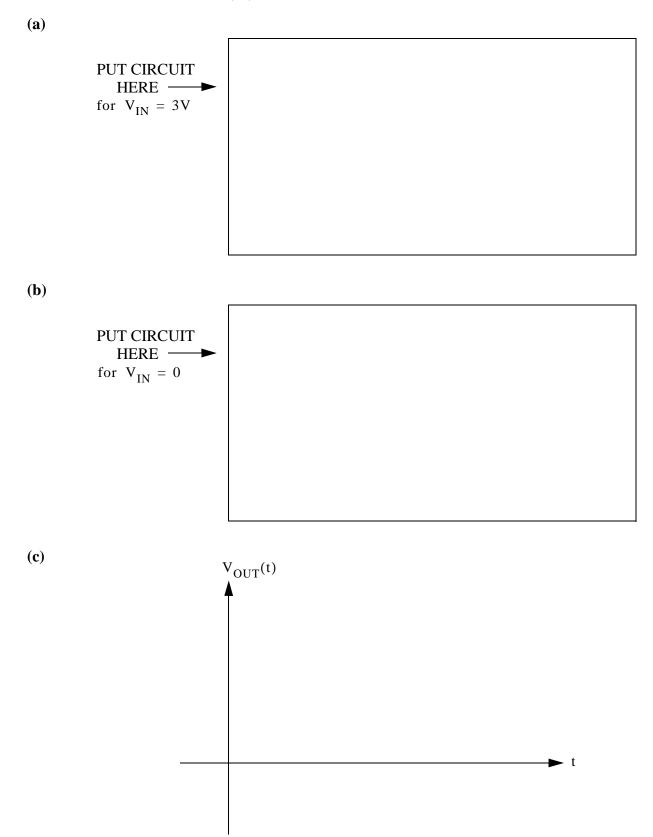

- (a) Draw the circuit model (in the box provided on opposite page) for the circuit (replacing transistors with appropriate simpler elements, such as voltage sources, current sources, resistors, capacitors, inductors) when  $V_{IN} = 3V$ . No numerical values are required in part (a).

- (b) Suppose  $V_{IN}$  suddenly switches to 0V at  $t = 0^+$ . Draw the new circuit model in the box provided (again with simpler elements). Show both the general form <u>and</u> the numerical values for all parameters.

- (c) Sketch the form of  $V_{OUT}$  versus time for  $t = 0^+$  to  $t \to \infty$  on the axes provided. (No numbers needed.)

- (d) What is the time delay for  $V_{OUT}$  to go to  $V_{DD}/2$  (in n sec)?

| Δt = | nsec |

|------|------|

|------|------|

(e) At what time does  $V_{OUT}$  equal 1 V (in n sec)?

#### Problem 5 (20 points)

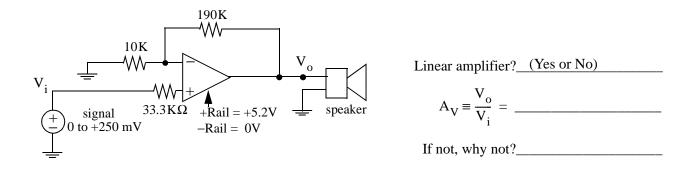

(a) You open up your Robot Kit and find the following circuit. You suspect it is a linear voltage amplifier. You know the differential amplifier has very high internal gain.

(a.1) Is it a linear amplifier?

(a.2) If so, what is the voltage gain  $\frac{V_o}{V_i}$ ? [If not, ignore (a.2).]

(a.3) If not, why not?

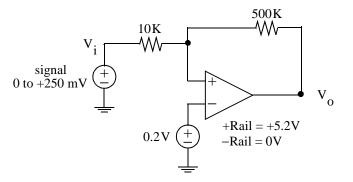

(b) You also find the following circuit. Again you suspect a linear amplifier. You know the differential amplifier has very high internal gain.

(**b.1**) Is it a linear amplifier?

(b.2) If so, what is the voltage gain? [If not, ignore (b.2).]

(**b.3**) If not, why not?

Linear amplifier? (Yes or No)  $A_V \equiv \frac{V_o}{V_i} =$

If not, why not?\_\_\_\_\_

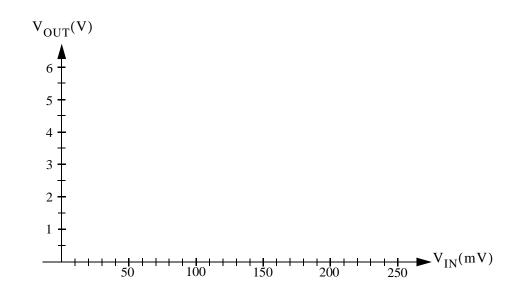

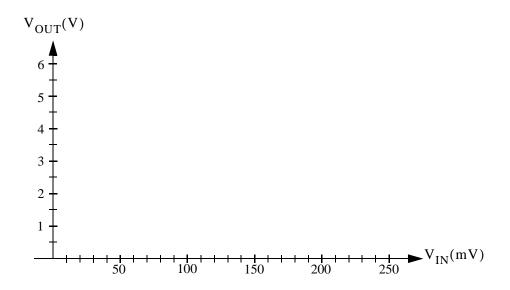

- (c) Carefully sketch the curve of  $V_{OUT}$  versus  $V_{IN}$  for circuit (a) on the graph axes provided for  $0 \le V_i \le 250 \text{mV}$ .

- (d) Carefully sketch the curve of  $V_{OUT}$  versus  $V_{IN}$  for circuit (b) on the graph axes provided for  $0 \le V_i \le 250 \text{mV}$ .

(c)

**(d**)