# UNIVERSITY OF CALIFORNIA

# College of Engineering Department of Electrical Engineering and Computer Sciences

EECS 40 Introduction to Microelectronic Circuits

Fall 2003 Prof. King

## **MIDTERM EXAMINATION #2**

November 3, 2003 Time allotted: 50 minutes

| NAME:                   | OLUTIO              | NS,First                                                  |

|-------------------------|---------------------|-----------------------------------------------------------|

| (print)                 | 11451               | T II St                                                   |

| Signature:              |                     | STUDENT ID#:                                              |

| Discussion Secti        | on:                 | <del></del>                                               |

| 1. This is a <b>CLO</b> | SED BOOK exai       | m. However, you may use 2 sheets of notes and a calculate |

|                         | R WORK or REA       | ASONING on this exam. the grader.)                        |

| 3. Write your an        | nswers clearly (le  | egibly) in the spaces (lines, boxes, or plots) provided.  |

| 4. Remember to s        | specify the units o | on answers whenever appropriate.                          |

|                         |                     |                                                           |

|                         | SCORE:              | 1/ 16                                                     |

|                         |                     | 2 / 17                                                    |

|                         |                     | 3/ 17                                                     |

|                         | Tota                | d: /50                                                    |

Problem 1: Energy-Storage Elements and 1st-Order Circuits [16 points in total]

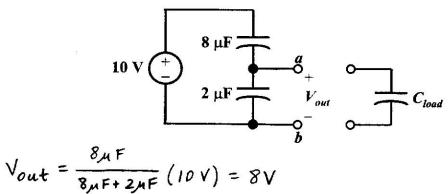

a) Consider the capacitive voltage-divider circuit below. Find  $V_{out}$ . How will  $V_{out}$  change if a small load capacitance  $C_{load} < 2 \mu F$  is connected between terminals a and b? [4 pts]

Vout =

$$\frac{1}{8\mu F + 2\mu F}$$

(10 V) = 8V

capacitance between terminals a and b

$V_{out} = 8 \text{ VoHs}$

$V_{out}$  will [increase, decrease] not change] (circle one) when  $C_{load}$  is connected, because

the capacitance between terminals a and b will increase.

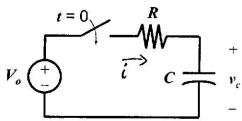

b) Consider the following RC circuit:

Provide a <u>physical</u> reason why it takes longer for  $v_c$  to reach its final value if R is increased. (Why is the characteristic time constant  $\tau$  proportional to R?) [2 pts]

$$i = \frac{V_0 - v_c}{R} = C \frac{dv_c}{dt}$$

$v_c$  will take longer to reach its final value if R is increased because

the current flowing through R (to charge C) will decrease, hence it will take longer to deliver the charge Q= CVo.

#### Problem 1 (continued)

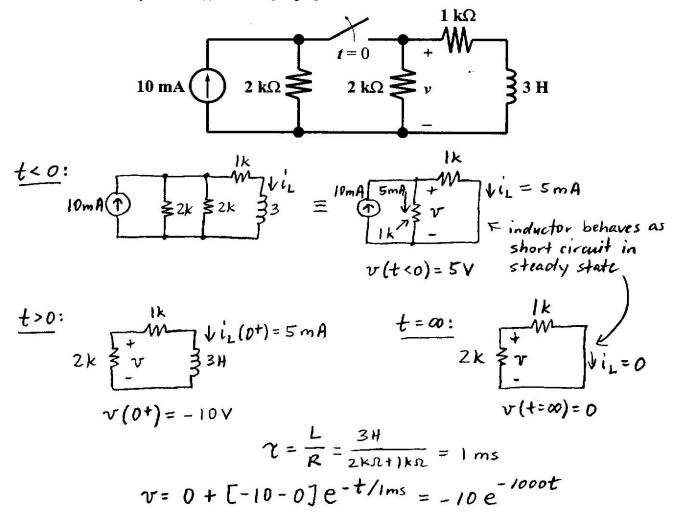

c) Assume that the circuit below is operating in steady state with the switch open for t < 0. Find and accurately sketch v(t) for all t. [10 pts]

For

$$t < 0$$

:  $v(t) = 5 \text{ V}$  For  $t > 0$ :  $v(t) = -1000 \text{ t}$

$$v(t) \text{ (Volts)}$$

$$10^{-3}$$

$$-10^{-3}$$

$$-3.6$$

### **Problem 2:** Semiconductor Materials and Devices [17 points in total]

- a) Consider a Si sample maintained at T = 300K, uniformly doped with Arsenic atoms to a concentration  $3 \times 10^{16}$  cm<sup>-3</sup>. The electron mobility = 1000 cm<sup>2</sup>/V\*s; hole mobility = 400 cm<sup>2</sup>/V\*s.

- i) Estimate the resistivity of this sample. (Use  $q = 1.6 \times 10^{-19}$  C in your calculation.) [4 pts]

As is a Column V element -> donor in Si

$$N_D = 3 \times 10^{16} \text{ cm}^{-3}$$

,  $N_A = 0 => n = 3 \times 10^{16} \text{ cm}^{-3}$ ,  $p = \frac{n_i^2}{n} \approx 3000$

$P = [g \mu_n n + g \mu_p p]^{-1} \approx [g \mu_n n]^{-1}$  since  $n >> p$

$P = [g \mu_n n + g \mu_p p]^{-1} \approx [g \mu_n n]^{-1} = [4.8]^{-1} \approx 0.2 \Omega - \text{cm}$

How will the resistivity of this sample change if it were to be doped additionally with  $3\times10^{16}$  cm<sup>-3</sup> Phosphorus atoms? [3 pts] carrier mobilities would be degraded.

P is also a Column V element  $\rightarrow$  donor in S:  $N_D = 6\times10^{16}$  cm<sup>-3</sup>,  $N_A = 0 = 0$  = 0 = 0 = 0 = 0

The resistivity will [increase, decrease] not change] (circle one)

by a factor that is [greater than, less than equal to] (circle one) 2 when phosphorus is added because

the number of conduction electrons will double, but un will decrease

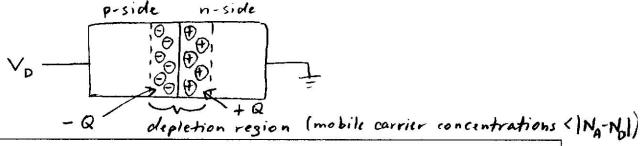

b) Explain (using 1 or 2 sentences) why a pn junction has capacitance. [2 pts]

A pn junction has capacitance because

charge is stored in the depletion region of a pn junction. The width of the depletion region, and hence the charge stored, varies with the bias voltage.  $C_j = |\frac{dQ}{dV_D}|$

## Problem 2 (continued)

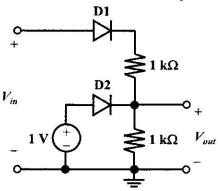

c) Assume the diodes in the circuit below can be modeled as perfect rectifiers.

For what values of  $V_{in}$  is D1 on? Explain your reasoning. [3 pts]

D1 is on for  $V_{in} > 1 \vee_{0} 1+ \cdots$  because forward current can flow in DI as long as Vin > Vout. DZ fixes Vont at IV, unless Vin causes Vont to be > 1 Volt.

For what values of  $V_{in}$  is D2 on? Explain your reasoning. [2 pts] ii)

D2 is on for  $V_{in} < 2 \text{ Vo Hs}$  because if Vin exceeds 2V, Vont will exceed I VoH and DZ will be reverse biased. (If D2 is on for Vin > 2V, reverse current would have to

For Vin < 2V, DZ is on and

iii)

For Vin > 2 V, DZ is off and

## Problem 3: MOSFET and Common-Source Amplifier [17 points in total]

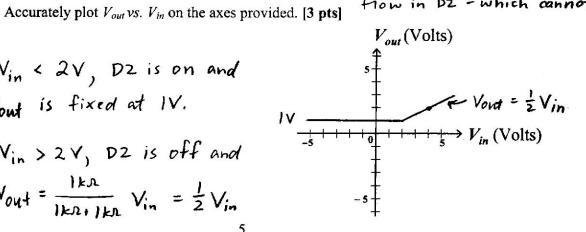

a) The following is the  $i_D$ - $v_{DS}$  characteristic of an n-channel MOSFET:

Indicate how this characteristic would change (by drawing the modified  $i_D$ - $v_{DS}$  characteristic with appropriate changes in  $I_{DSAT}$  and  $V_{DSAT}$ ):

i) when  $V_T$  is lowered – use a labeled solid line on the plot above [2 pts]

$$I_{DSAT} = k' \frac{W}{2L} (V_{GS} - V_T)^2$$

increases

$V_{DSAT} = V_{GS} - V_T$  increases

slope at small  $V_{DS} = k' \frac{W}{L} (V_{GS} - V_T - \frac{V_{DS}}{2})$  increases

ii) when channel-length modulation is significant – use a labeled dashed line on the plot above [2 pts]

iii) when the current is limited by velocity saturation, rather than pinch-off – use a labeled dotted line on the plot above [2 pts]

$$V_{DSAT} = \frac{L}{M} v_{sat} < V_{GS} - V_{T}$$

(decreases)

$I_{DSAT}$  decreases

.

slope at small vos unchanged

#### Problem 3 (continued)

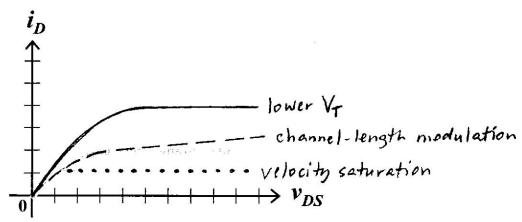

**b)** Below to the left is the  $i_D$  vs.  $v_{DS}$  characteristic for a long n-channel MOSFET with  $V_T = 1$  V.

$$V_{DSAT} = V_{AS} - V_{T}$$

3 =  $V_{AS} - 1$  =>  $V_{AS} = 4V$

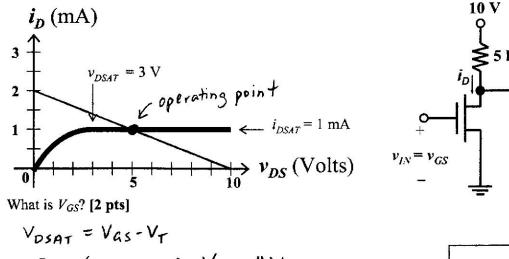

- c) Suppose the MOSFET in part (b) is used in the amplifier circuit shown above to the right.

- Draw the load line on the MOSFET  $i_D$ - $v_{DS}$  plot (above to the left). [3 pts]

- In what region is the MOSFET operating? [2 pts]

The MOSFET is operating in the [linear, saturation] cutoff] (circle one) region because VDS > VDSAT and iD > 0

What is the incremental change in the output voltage (i.e.  $v_{out}$ ) for a -1 mV change in the iii) input voltage (i.e.  $v_{gs} = -1 \text{ mV}$ )? [4 pts]

$$g_{m} = \frac{\partial i_{D}}{\partial v_{GS}} = \frac{\partial}{\partial v_{GS}} \left[ k' \frac{w}{2L} (V_{GS} - V_{T})^{2} \right]$$

$$= k' \frac{w}{L} (V_{GS} - V_{T})$$

$$= \frac{z}{9} \frac{mA}{V^{2}} \times 3V = \frac{z}{3} mS^{7}$$

$$i_{DSAT} = k' \frac{W}{2L} (V_{4S} - V_T)^2 = ImA$$

=  $i_{DSAT} = k' \frac{W}{2L} (3)^2 = ImA$

$k' \frac{W}{L} = \frac{2}{9} mA/V^2$

$$V_{out} = -g_m V_{gs} (5k\pi)$$

=  $-\frac{2}{3} \times 10^{-3} (-10^{-3})(5 \times 10^3)$

$V_{out} = 3.3 \text{ mV}$