## EE143 Midterm #2 Solutions

**Problem 1**

(a) E-Beam lithography has to address and expose the pixels in a serial fashion. Optical lithography can expose all pixels simultaneously by flood exposure ( a parallel process). The later has a higher throughput.(b)

(i) AZ1350J is a positive resist .Kodak 747 is a negative resist.

(ii) For positive resist (AZ1350J),

$$\gamma = \frac{1}{\log 10(90/45)} = 3.32$$

For negative resist (Kodak 747),  $\gamma = \frac{1}{\log 10(12/7)} = 4.27$  (higher resist contrast)

(iii) Resist Kodak 747 (better sensitivity) only needs 12mJ/cm2 to fully exposure while AZ13750J requires 90 mj/cm2 to fully expose.

(c )Technology factors:  $k_1 = 0.58$  and  $k_2 = 0.54$

$$L_{min} = k_1 \times 248 nm / 0.5 = 0.28 \ \mu m$$

$DOF = k_2 x \ 248 nm/(0.5)^2 = 0.53 \mu m$

- (d) Steppers maintained at constant temperature to minimize thermal run-in/out overlay errors due to different thermal expansion coefficients of mask and substrate.

- (e) To reduce difference of standing wave's I  $_{max}$  and I  $_{mjn}$ , one can use a resist with absorption dyes or by placing an antireflection coating on the reflecting interface.

## Problem 2

(a)  $C_T(Sid_4) = 0.02x4.8 \text{ xl}0^{18} = 9.6 \text{ xl}0^{16} \text{ molecules/cm}^3$ Since 1 molecule of SiCl<sub>4</sub> gives 1 Si atom and the growth rate is assumed to mass-transfer limited,

$$\therefore \frac{dy}{dt} == \frac{1}{\left(\frac{1}{k_s} + \frac{1}{h_G}\right)} \cdot \frac{C_T}{5x10^{22}} \approx \frac{h_G C_T}{5x10^{22}} = \frac{2.62x9.6x10^{16}}{5x10^{22}} = 5.03x10^{-6} \text{ cm/sec} = 503 \text{ Å/sec}$$

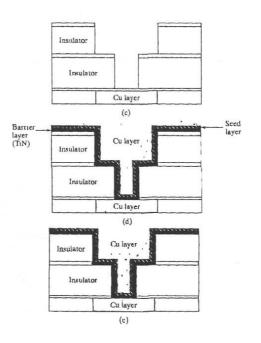

(b) (i) We will use the linear regime of the curve where surface-reaction mechanism determines the growth rate R

R = constant x exp[-E<sub>a</sub>/kT] or E<sub>a</sub> =-1000 k ×

$$\frac{\ln R(1) - \ln R(2)}{1000/T(1) - 1000/T(2)}$$

R = 0.2 µm/min at 1000/T =0.93 and R = 0.01 µm/min at 1000/T = 1.1

Therefore E<sub>a</sub> = -1000 x 8.617 x10<sup>-5</sup>×  $\frac{\ln(0.2) - \ln(0.1)}{0.93 - 101}$  = **1.5eV**.

(ii) The SiH4 concentration  $C_T$  is lower due to the lower partial pressure of SiH4. Therefore R will lower for both mass transfer and surface reaction limited regions

The  $k_s$  term is not affected by the dilution effect.

The h<sub>G</sub> term (=

$$D/\overline{\delta}$$

) will have no change in D ( $\propto \frac{T^{3/2}}{P}$ ) because P<sub>tolal</sub> is same. The  $\overline{\delta}$  term =  $\frac{2L}{3\sqrt{\frac{\rho UL}{\mu}}}$  will

have minor changes in density and viscosity due to He dilution but will be second-order.

(c) (i) Step coverage problem is due to directional flux used for deposition (e.g. sputtering). Since the spherical receiving surface will be making different angles to the wafer surface for different r positions, we will still see step

(ii) Coverage effects. (ii) Flux arriving at wafer distance r F'  $\propto (\cos \theta)^2 / r^2$ Thickness deposited on wafer  $\propto F' x \cos \Phi$  (with  $\Phi = \theta$ )  $\propto (\cos \theta)^3 / r^2$ Since  $\cos \theta = (r/2)/R$ , therefore **thickness**  $\propto r$ .

## Problem 3

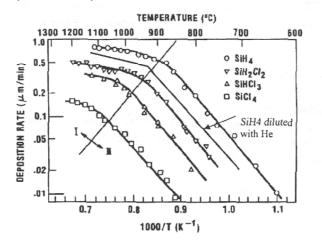

(iii)

(A) At release time = 2 min, Method (ii) has a larger gap of clearance than Method (i). Less stiction problem.to release the beam.

(B) For a given required clearance, Method (ii) takes less wet etch time

(C) The larger cleared gap between t = 2 to 4 min can assist the HF etch solution to give more vertical etching component above the spike regions, giving a slightly more planar substrate surface.

(b) Overetch fraction time over step  $\Delta = 7000/4000 = 1.75$

Worst-case etching time

$$t = \frac{h_f}{v_f} \times \frac{(1+\delta)(1+\Delta)}{(1-\Phi_f)} = \frac{h_f}{v_f} [(1+0.03)(1+1.75)/(1-0.05)] = \frac{h_f}{v_f} \times 2.98$$

Mask erosion W/2 = vm x  $\cot \theta$  x t

Minimum etching selectivity of poly-Si to mask  $S_{fm} = \frac{v_f}{v_m} = \frac{4000}{1000/2} [\cot 80^\circ] \times 2.98 = 4.2$

(c) (i)  $O_2$  addition to  $CF_4$  plasma will generate more  $F^*$  radical which will etch Si faster. This chemical etching component is isotropic in nature.

(ii) Substrate bombardment by vertically directed energetic ions can sputter away deposited polymer and also damage the substrate atoms at bottom area. Both effects will increase the vertical etching rate compared with the lateral sidewall etching rate.

## **Problem 4**

(a)\_\_\_+\_\_\_ Use a wet chemical etch for the contact holes

Explanation: Wet etch is isotropic. Contact hole has gentler slope.

\_\_\_\_+\_\_\_Increase substrate temperature **during** Al deposition

*Explanation: Surface diffusion is enhanced with higher temperature which evens out thickness variation.* - Thicken the oxide around the contact holes while keeping contact size same

*Explanation: More shadowing effect with higher aspect ratio of the contact hole*

+\_\_\_\_Develop a CVD Al process

Explanation: CVD is more conformal than evaporation and sputtering

\_\_\_\_+\_\_\_Fill the contact hole with CVD tungsten plug before Al deposition

Explanation: The W plug will planarize the contact hole

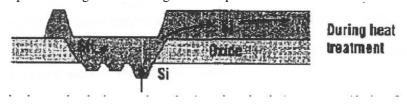

(b) (i) Dissolution of Si into Al is easier at regions with localized "defects" (e.g. pinholes in the residual native oxide left by contact hole cleaning or Al grain boundaries). The localized Ai-Si reactions will form spikes instead of a uniform interfacial reaction.

(ii) Perimeter of contact holes is closer to the Al interconnect which has a length much larger than the contact hole size. The volume of Al in the interconnect acts like a large reservoir to induce more Si dissolution. Therefore the spikes forms near the perimeter region will be larger and deeper.

(iii) If the Al spike has a depth deeper than the junction depth (e.g. source/drain of a MOSFET), it will form a Schottky ohmic contact with the p-type substrate, shorting the source/drain contact to substrate.(c) Al-Cu alloy during the sintering step at 400C will precipitate out at the grain boundaries of the interconnect, blocking the grain boundary diffusion paths for the electromigrated Al atoms. MTF will improve.

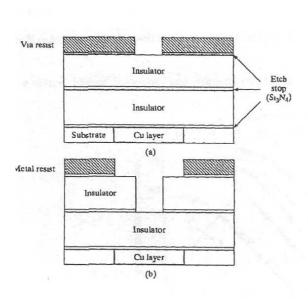

(d) Key ideas of dual damascene process flow: 2 layers of dielectrics  $\rightarrow$  contact via patterning -» interconnect patterning (larger than contact via size)  $\rightarrow$  Cu deposition  $\rightarrow$  planarized by CMP.

To improve the process latitude and performance, one can add etch stops between dielectric layers, encapsulate all copper by depositing diffusion barrier films before Cu deposition which can also serve as a seed layer for Cu plating if copper plating is used.