University of California College of Engineering Department of Electrical Engineering and Computer Sciences

E. Alon

Tuesday, October 7, 2008 6:30-8:00pm

## EECS 141: FALL 2008-MIDTERM 1

For all problems, you can assume that all transistors have a channel length of 100nm and the following parameters (unless otherwise mentioned):

**NMOS:**   $V_{Tn} = 0.2V, \ \mu_n = 400 \ \text{cm}^2/(\text{V}\cdot\text{s}), \ \text{C}_{\text{ox}} = 1.125 \ \mu\text{F/cm}^2, \ v_{\text{sat}} = 1e7 \ \text{cm/s}, \ \lambda = 0$  **PMOS:**  $|V_{Tp}| = 0.2V, \ \mu_p = 200 \ \text{cm}^2/(\text{V}\cdot\text{s}), \ \text{C}_{\text{ox}} = 1.125 \ \mu\text{F/cm}^2, \ v_{\text{sat}} = 1e7 \ \text{cm/s}, \ \lambda = 0$

|--|

|  | GRAD/UNDERGRAD |  |

|--|----------------|--|

|--|----------------|--|

- Problem 1: \_\_\_\_/ 18

- Problem 2: \_\_\_\_/ 20

- Problem 3: \_\_\_\_/ 26

- Total: \_\_\_\_/ 64

## **PROBLEM 1. (18 pts) Complex Gates and Elmore Delay.**

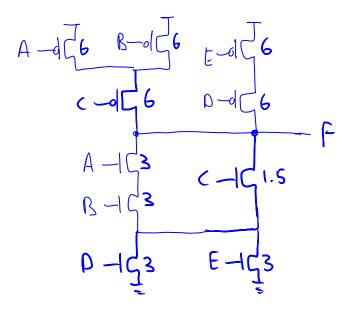

a) (6 pts) Implement the function  $F = (\overline{A \cdot B + C}) \cdot (\overline{D + E})$  with a complex static CMOS gate. Assuming  $R_{sqp} = 3R_{sqn}$ , you should size your gate so that the worst-case pull up resistance is equal to the worst-case pull-down resistance.

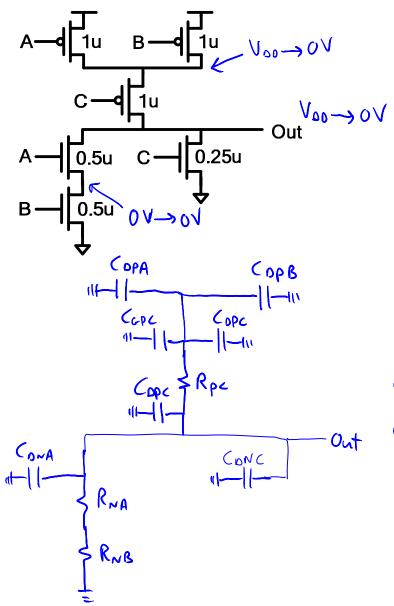

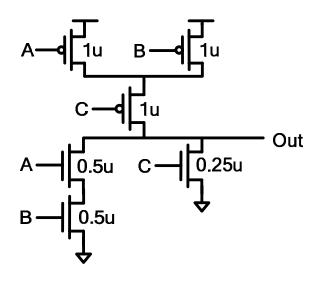

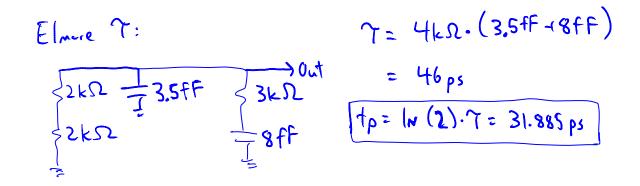

b) (6 pts) Using the switch model for the transistors, draw the RC network you would use to calculate the delay of the gate shown below when  $B = V_{DD}$ , C = 0V, and A transitions from 0V to  $V_{DD}$ . You can assume that  $C_G = C_D = 2fF/\mu m$ ,  $R_{sqn} = 10k\Omega/\Box$ , and  $R_{sqp} = 30k\Omega/\Box$ .

$$R_{NB} = R_{NA} = 10k \Omega \cdot \frac{l_{Jum}}{s_{Jum}} = 2k \Omega$$

$$C_{ONA} = 2fF/Jum \cdot 0.s_{Jum} = lfF$$

$$C_{ONC} = 2fF/Jum \cdot 0.2s_{Jum} = 0.sfF$$

$$C_{OPC} = C_{OPB} = C_{OPA} = C_{OPC} = 2fF$$

$$R_{PC} = 30k \Omega \cdot \frac{l_{Jum}}{J_{Jum}} = 3k \Omega$$

c) (6 pts) Using the same model and component values you drew in part b), what is the delay of the gate under the same situation (i.e., when  $B = V_{DD}$ , C = 0V, and A transitions from 0V to  $V_{DD}$ )? You should provide your answer for the delay in both absolute ps and in units of  $t_{inv}$ . For your convenience the gate has been repeated below.

$$\frac{4iNV}{\frac{3}{2}} = \frac{1}{100} \frac{1}{$$

## PROBLEM 2. (20 pts) IV Characteristics, VTCs, and Energy

a) (2 pts) For a long-channel (quadratic) NMOS transistor with  $V_{GS} = V_{DS} = 1.2V$ , how does the drain current change if the mobility of the device  $\mu_n$  is doubled? How about if  $C_{ox}$  is doubled?

b) (6 pts) Now let's look at a short-channel (velocity-saturated) NMOS transistor with  $V_{GS} = V_{DS} = 1.2V$ . Using the velocity saturated model for this transistor, how much drain current would you get from a 1µm wide transistor if you doubled  $\mu_n$  to 800 cm<sup>2</sup>/(V·s)? How about if you doubled C<sub>ox</sub> to 2.25 µF/cm<sup>2</sup>?

$$T_{N} = v - s_{N} t; \quad T_{0N} = W u_{soft} \left( u_{s} - v_{TH} \right)^{2} \frac{\left( v_{0s} - v_{TH} + E_{c} L \right)}{\left( v_{0s} - v_{TH} + E_{c} L \right)}$$

First let's calculate original  $E_{c} = \frac{2u_{s} t}{M_{N}} = 50 \text{ kV/cm}$

$$S_{s} = 0.5 \text{ V} \quad D_{cable} \quad M_{N} : \quad E_{c} L = 0.25 \text{ V}$$

$$\frac{D_{cable} \quad M_{N} :}{T_{0} = l_{\mu}m \cdot le7} \text{ cm} l_{s} \cdot 1.125 \, \mu F l_{c}m^{2} \cdot \frac{\left(1.2 \text{V} - 0.2 \text{V}\right)^{2}}{\left(1.2 \text{V} - 0.2 \text{V} + 0.25 \text{V}\right)}$$

$$I_{0} = \frac{900 \, \mu \text{A}}{I_{0}}$$

$$\frac{D_{ouble} \quad (cx)}{T_{0} = l_{\mu}m \cdot le7} \text{ cm} l_{s} \cdot 2.25 \, \mu F l_{c}m^{2} \cdot \frac{\left(1.2 \text{V} - 0.2 \text{V}\right)^{2}}{\left(1.2 \text{V} - 0.2 \text{V} + 0.5 \text{V}\right)}$$

$$T_{D} = 1.5 \, \text{m} \text{A}$$

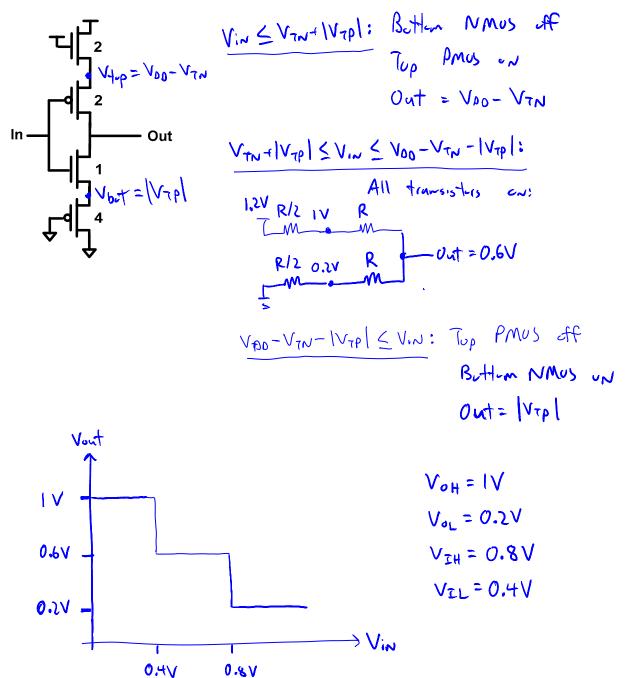

c) (6 pts) For parts c) and d), you should use the simple switch model of the transistors with  $R_{sqn} = 10k\Omega/\Box$ ,  $R_{sqp} = 20k\Omega/\Box$ ,  $V_{DD} = 1.2V$ , and  $V_{TN} = |V_{TP}| = 0.2V$ . Draw the VTC of the circuit shown below and provide the values of  $V_{OH}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{IL}$ .

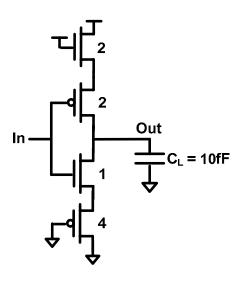

d) (6 points) For this same circuit (repeated below), how much energy is supplied by  $V_{DD}$  to charge  $C_L$  when In steps from  $V_{DD}$  to 0V?

When

$$T_{r}$$

steps from  $V_{00}$  to

$OV$ ,  $Out$  goes from  $V_{01} \rightarrow V_{04}$ :

$\Delta V = IV - 0.2V = 0.8V$

So, charge pulled from supply is:

$Q = C_1 \cdot \Delta V = 10 \text{ FF} \cdot 0.8V = 8\text{ FC}$

and:

$E = V_{00} \cdot Q = 1.2V \cdot 8\text{ FC}$

$[E = 9.6 \text{ FJ}]$

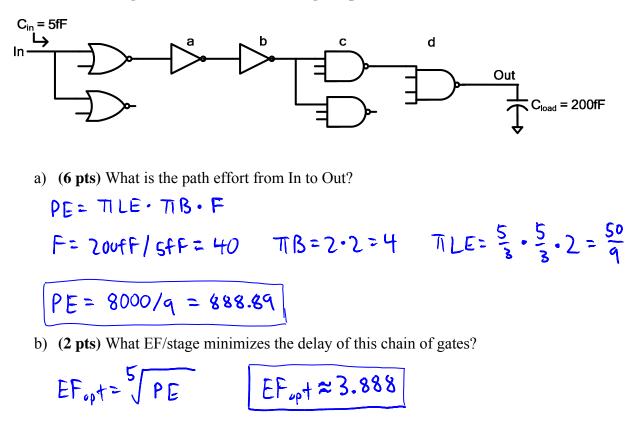

## **PROBLEM 3. Logical Effort and Gate Sizing (26 points)**

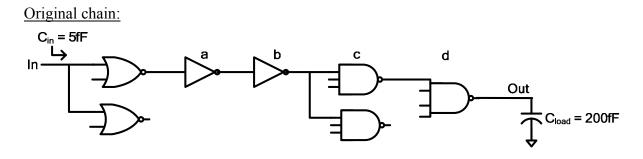

c) (8 pts) Size the gates to minimize the delay from In to Out.

$$\frac{200fF}{d} \cdot 2 = 3.888 \quad d \approx 102.88 \, \text{ff}$$

$$\frac{d}{c} \cdot \frac{5}{3} = 3.888 \quad c \approx 444.1 \, \text{ff}$$

$$\frac{c}{b} \cdot 2 = 3.888 \quad b \approx 22.64 \, \text{ff}$$

$$\frac{b}{a} = 3.888 \qquad a \approx 5.84 \, \text{ff}$$

| Size | Value (fF) |

|------|------------|

| a    | 5.84       |

| b    | 22.69      |

| c    | 44.1       |

| d    | 102.88     |

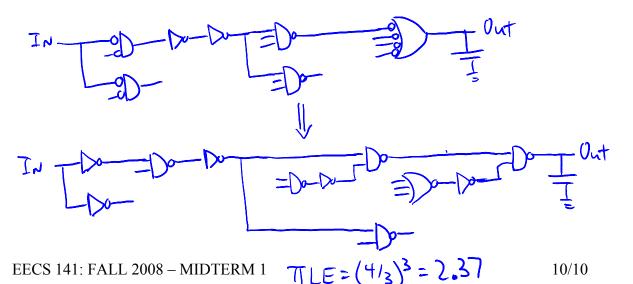

d) (4 pts) By changing only the order (but not the types) of the gates, can you reduce the total capacitance of the gates in this chain? If so, draw the re-ordered chain (you do not need to recalculate the sizes) and explain why the capacitance is reduced; if not, explain why this isn't possible.

The complex gutes arent very good drivers, so for the same EF they need to be substantially larger than an inverter. By moving the complex gates earlier, their capacitance is reduced by quite a bit more than the cap. of the inverters (which are moved closer to the final load) increases. e) (6 points) While maintaining the same logical functionality and without changing C<sub>in</sub>, can you improve the delay of this chain of gates (repeated below) by changing the number and/or types of gates? Please draw an improved schematic for the new chain of gates; you don't need to provide gate sizes.

Improved chain:

Since EF/stage is already cluse 4, don't really need to charge # of stages - best bet is to reduce LE by moving logic off path and reducing gate complexity. Can also charge NUR to NAND. Any logically equivalent solution with reduced LE will receive full credit; one possibility (and the transformations used to reach it) is shown below.