University of California College of Engineering Department of Electrical Engineering and Computer Sciences

E. Alon

Tuesday, November 6, 2007 6:30-8:00pm

## EECS 141: FALL 2007-MIDTERM 2

For all problems, you can assume the following transistor parameters (unless mentioned otherwise):

**NMOS:**   $V_{Tn} = 0.4, k'_n = 115 \,\mu\text{A/V}^2, V_{DSAT} = 0.6\text{V}, \lambda = 0, \gamma = 0.4 \,\text{V}^{1/2}, 2\Phi_F = -0.6\text{V}$  **PMOS:**  $V_{Tp} = -0.4\text{V}, k'_p = 30 \,\mu\text{A/V}^2, V_{DSAT} = -1\text{V}, \lambda = 0, \gamma = -0.4 \,\text{V}^{1/2}, 2\Phi_F = 0.6\text{V}$

|--|

| GRAD/UNDERGRAD |

|----------------|

|----------------|

- Problem 1: \_\_\_\_/20

- Problem 2: \_\_\_\_/22

- Problem 3: \_\_\_\_/17

- Total: \_\_\_\_/59

## **PROBLEM 1.** Wires and Elmore Delay (20 points)

For this problem, you should assume that all of the transistors are minimum channel length (L=0.25µm) and have the following characteristics:  $C_G = 2fF/\mu m$ ,  $C_D = 1fF/\mu m$ , and  $R_{sqn} = R_{sqp}/2 = 15k\Omega/\Box$ . For the wires, you should assume that  $C_{wpp} = 0.1fF/\mu m^2$ ,  $C_{wfringe} = 0.05fF/\mu m/edge$ , and  $R_w = 0.1\Omega/\Box$

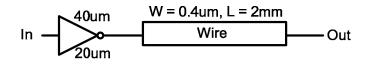

a) (5 pts) Draw the RC model you would use to calculate the delay of the circuit shown above from In rising to Out falling. You should replace the wire with a single section  $\Pi$  model and calculate the values of the R's and C's in your model.

b) (3 pts) Using this model and assuming a ramp input (i.e.,  $t_p = \tau_{Elmore}$ ), what is the delay from In rising to Out falling?

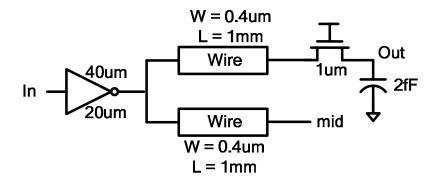

c) (12 pts) What is the ramp delay from In rising to Out falling for the circuit shown above? You do not need to provide a numerical answer for this problem – you only need to provide the equation you would use to calculate the delay, and the values of the R's and C's in that equation. You can assume that Out is initially charged to  $V_{DD}$ , and you can model each of the wires with a single section  $\Pi$  model.

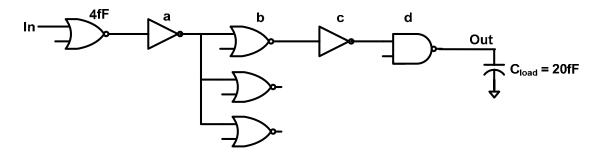

**PROBLEM 2.** Logical Effort and Gate Sizing (22 points)

a) (6 pts) What is the path effort from In to Out?

b) (2 pts) What EF/stage minimizes the delay of this chain of gates?

c) (8 pts) Size the gates to minimize the delay from In to Out.

| Size | Value (fF) |

|------|------------|

| a    |            |

| b    |            |

| c    |            |

| d    |            |

d) (6 pts) Both the delay and the power consumption of this gate chain of gates can be reduced by changing the number of stages and/or the types of gates used in the chain (but still implementing the same logic function). Please draw an improved (from both a power and delay standpoint) schematic for this chain of gates. You do not need to provide transistor sizes. (Hint: What would be the optimal number of stages for a chain of gates with the path effort you calculated?)

## **PROBLEM 3. Logic Styles (17 points)**

a) (6 pts) Implement the function  $F = (A \cdot B) + (C+D) \cdot E$  with a complex static CMOS gate. You should arrange your gate to minimize the delay from the E input, and so that the worst-case pull up resistance is equal to the worst-case pull-down resistance.

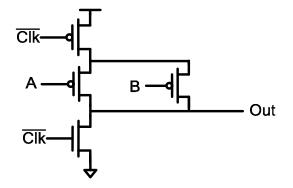

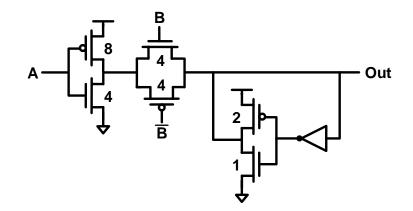

b) (3 pts) What is the logic function performed by the dynamic gate shown below?

c) (8 pts) What is the LE of the gate shown above from the B input?