# University of California College of Engineering Department of Electrical Engineering and Computer Sciences

E. Alon

Thursday, October 4, 2007 6:30-8:00pm

## EECS 141: FALL 2007—MIDTERM 1

For all problems, you can assume the following transistor parameters (unless otherwise mentioned):

| TA TTA  | <i>T</i> | ``  |

|---------|----------|-----|

|         | /        |     |

| 1 7 1 7 |          | ハフ・ |

$$V_{Tn} = 0.4, k'_n = 115 \ \mu\text{A/V}^2, V_{VSAT} = 0.6 \text{V}, \lambda = 0, \gamma = 0.4 \ \text{V}^{1/2}, 2|\Phi_F/=0.6 \text{V}$$

**PMOS:**

$$|V_{Tp}| = 0.4 \text{V}, |k'_p| = 30 \text{ } \mu\text{A/V}^2, |V_{VSAT}| = 1 \text{V}, \lambda = 0, |\gamma| = 0.4 \text{ } \text{V}^{1/2}, 2\Phi_F = 0.6 \text{V}$$

| NAME     | Last Solutions | First |  |

|----------|----------------|-------|--|

|          |                |       |  |

| GRAD/UNI | DERGRAD        |       |  |

**Problem 1: \_\_\_\_/26**

**Problem 2: \_\_\_\_/16**

**Problem 3: \_\_\_\_/ 10**

**Total:** / 52

#### PROBLEM 1. (26 pts) Dynamic Inverters: VTC and Delay.

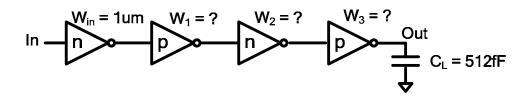

For this problem only, you should assume that  $R_{sq,p} = R_{sq,n} = R_{sq}$ . In other words, an inverter with  $W_p = W_n = 1\mu m$  would have equal rising and falling delays. Note that this means that  $t_{inv} = 2 \cdot \ln(2) \cdot L \cdot R_{sq} \cdot C_G$ . Also,  $V_{DD} = 2.5V$ .

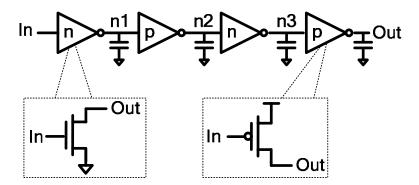

The figure above shows a chain of 4 dynamic "inverters"; every cycle, before the inverters are used, their outputs are set to a well-known state through transistors not shown here (which you can assume are negligibly small compared to the transistors in the inverter). Specifically, for an "n" dynamic inverter, its output starts at  $V_{DD}$  (2.5V), and for a "p" dynamic inverter the output starts at Gnd (0V). So, in the figure above, nodes "n1" and "n3" would be initially charged to  $V_{DD}$ , and nodes "n2" and "Out" would be initially discharged to Gnd (0V). Once these initial voltages have been set, no transistors drive the output until there is a rising transition at the input of an n inverter, or a falling transition at the input of a p inverter. In other words, the inverter's output voltage is simply stored on the capacitance at its output.

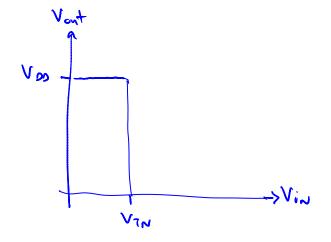

a) (3 pts) Please draw the VTC of an n dynamic inverter as its input is swept from 0V to  $V_{DD}$ . Remember that the output of an n inverter is initially charged to  $V_{DD}$ . Please also provide the values of  $V_{OL}$ ,  $V_{IH}$ , and  $V_{IL}$ .

$$V_{\text{off}} = V_{00} = 2.5$$

$V_{\text{ol}} = 0$   $V_{\text{IH}} = V_{\text{TN}} = 0.4$   $V_{\text{IL}} = V_{\text{TN}} = 0.4$

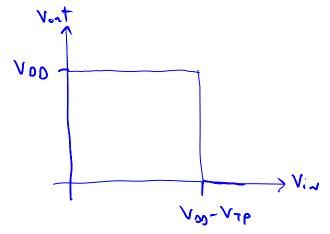

b) (3 pts) Please draw the VTC of a p dynamic inverter as its input is swept from  $V_{DD}$  to 0V. Remember that the output of a p inverter is initially discharged to Gnd. Please also provide the values of  $V_{OH}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{IL}$ .

$$V_{cH} = V_{0D} = 2.5V$$

$V_{0L} = 0V$

$V_{ZH} = V_{00} - V_{TP} = 2.1V$

$V_{ZL} = V_{00} - V_{TP} = 2.1V$

c) (4 pts) Now we'll look at the sizing of a chain of such dynamic inverters. Using the RC model, write an equation for the delay of an n inverter of width W driving a fixed capacitance  $C_L$  with a rising step (0  $\rightarrow$   $V_{DD}$ ) at its input. Your expression for the delay should be in terms of W, L,  $R_{sq}$ ,  $C_L$ ,  $C_G$  (effective gate capacitance per  $\mu$ m of width), and  $C_D$  (effective diffusion capacitance per  $\mu$ m of width).

$$C_{tot} = C_{L} + WC_{0}$$

$$R_{inv} = R_{sq} \cdot \frac{L}{W} \cdot (C_{L} + WC_{0})$$

$$C_{tot} = C_{L} + WC_{0}$$

d) (6 pts) Noting that the delay of a p inverter will follow the same equation you derived in part c) for the delay of an n inverter, and assuming  $C_G = 1.5 \text{fF/}\mu\text{m}$ , size the buffer chain shown above to minimize its delay from In rising to Out rising.

$$C_{in} = 1.5 ff$$

$C_{L}/C_{in} = 512 ff / 1.5 ff = 341.33$

$f = 4 \int C_{L}/C_{in} = 4.298 \approx 4.3$

$W_{1} = fw_{in}$

$W_{2} = f^{2} w_{in}$

$w_{3} = f^{3} w_{in}$

| Width          | Value (µm) |

|----------------|------------|

| $\mathbf{W}_1$ | 4.3        |

| $W_2$          | 18.49      |

| $W_3$          | 79.5       |

e) (4 pts) Using your sizing and assuming  $\gamma = C_D/C_G = 0.5$ , what is the delay of this inverter chain? Please provide your delay in units of  $t_{inv} = 2 \cdot \ln(2) \cdot L \cdot R_{sq} \cdot C_G$ .

$$t_p = N + dinv \left( x + f \right)$$

$$t_{dinv} = \ln(2) \operatorname{Rsy} C_b L = \frac{1}{2} + inv$$

$$t_p = 4 \cdot \frac{1}{2} \cdot (0.5 + 4.3)$$

$$t_p = 9.6 + inv$$

f) (6 pts) For a constant C<sub>L</sub>/C<sub>in</sub>, would the optimum number of stages for minimum delay with standard inverters be larger, smaller, or the same as the optimum number of stages for a chain of these dynamic inverters? Which chain would have lower delay? Be sure to explain your answers. If you are unsure about the answers to this question, you may want to complete the rest of exam and come back to this later.

The number of stuyes would stay the same, because N is set only by Culcin and X-neither of which have changed. The delay of the dynamic inverter chain would be half the delay of the stundard chain though, be cause thin = \frac{1}{2} \times time.

#### PROBLEM 2. (16 pts) IV Characteristics and Power Consumption

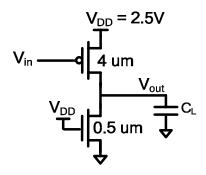

For this problem, all transistors are minimum channel length (i.e.,  $L = 0.25 \mu m$ ).

a) (6 pts) Using the unified transistor IV model, how much current flows from  $V_{DD}$  to Gnd when  $V_{in} = 0V$ ? (Hint: Think about the regions of operation – which transistor would have more current if both devices were velocity saturated?)

Since Wp>) Wn, if both transistors were velocity saturated, the PMOS would have more current. So, in order for Iop to equal Ion, the PMOS can not be velocity saturated (it will be linear). The nmos device will be relocity saturated, and therefore it sets the current:

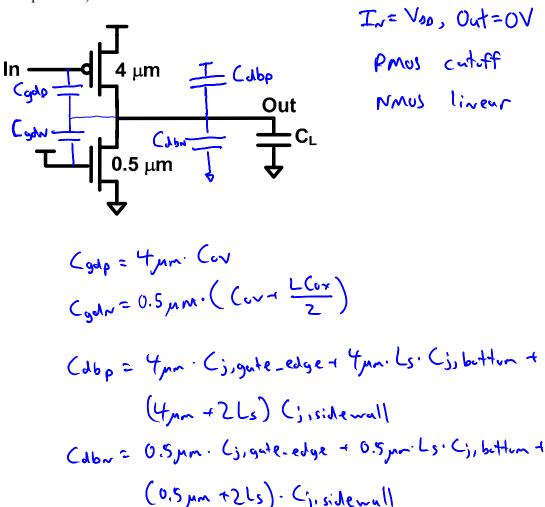

b) (6 pts) Using the detailed model of transistor capacitance discussed in Lecture 7, please draw all of the capacitors connected to Out when  $V_{in} = V_{DD}$  on the figure below. You should also write out the equations you would use to calculate the values of these capacitors – these equations should be in terms of  $C_{ox}$ ,  $C_{ov}$ , L,  $L_{S}$ ,  $C_{j,bottom}$ ,  $C_{j,sidewall}$ ,  $C_{j,gate\_edge}$ , and the widths of the transistors. (Note that you do not need to plug in any numbers for these parameters – only write out the equations.)

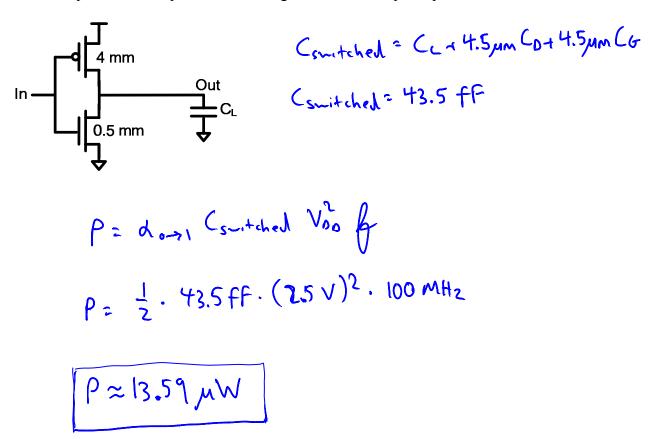

c) (4 pts) Now using the simplified capacitance model with  $C_G = 2 f F/\mu m$  and  $C_D = 1 f F/\mu m$ , how much dynamic power would a standard CMOS inverter with the same sizing (shown below) consume if In transitions from 0 to 1 every other clock cycle, the clock frequency is 100MHz, and  $C_L = 30 f F$ ? Don't forget to include the power consumption from driving the inverter's input capacitance.

### PROBLEM 3. (10 pts) Scaling.

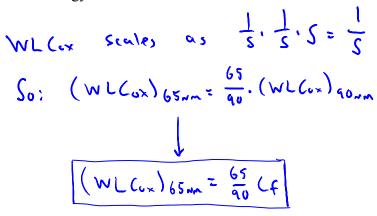

a) (5 pts) Let's assume that the capacitive load that sets the delay of an inverter is  $C_L$ , where  $C_L = WLC_{ox} + C_f$ , and  $C_f$  does not scale with technology. If in a 90nm technology  $WLC_{ox}$  is equal to  $C_f$ , what would  $WLC_{ox}$  be (in terms of  $C_f$ ) in a 65nm technology?

b) (5 pts) Given your answer to part a), how would the delay of an inverter with this C<sub>L</sub> scale from 90nm to 65nm?