University of California College of Engineering Department of Electrical Engineering and Computer Sciences

B. Nikolić

Thursday, November 7, 2002 6:00-7:30pm

# EECS 141: FALL 2002-MIDTERM 2

For all problems, you can assume the following transistor parameters (unless mentioned otherwise): NMOS:

$V_{Tn} = 0.4, k'_n = 115 \,\mu\text{A/V}^2, V_{DSAT} = 0.6 \text{V}, \lambda = 0, \gamma = 0.4 \,\text{V}^{1/2}, 2\Phi_F = -0.6 \text{V}$  **PMOS:**  $V_{Tp} = -0.4 \text{V}, k'_p = 30 \,\mu\text{A/V}^2, V_{DSAT} = -1 \text{V}, \lambda = 0, \gamma = -0.4 \,\text{V}^{1/2}, 2\Phi_F = 0.6 \text{V}$

| Last First |

|------------|

|------------|

| GRAD/UNDERGRAD |  |

|----------------|--|

|----------------|--|

- Problem 1: \_\_\_\_/16

- Problem 2: \_\_\_\_/12

- Problem 3: \_\_\_\_/10

- Problem 4: \_\_\_\_/ 6

- Total: \_\_\_\_/44

## **PROBLEM 1. Logic Styles (16pts)**

In this problem, for single-ended logic styles, assume that only true inputs are available, and for differential logic styles you can use both true and complementary inputs. Draw a gate implementing Y = AB + CD in:

a) Standard complementary CMOS.

b) Domino logic.

c) Dual-rail domino.

d) Transmission-gate logic (differential logic style)

# **PROBLEM 2. Logical effort. (12pts)**

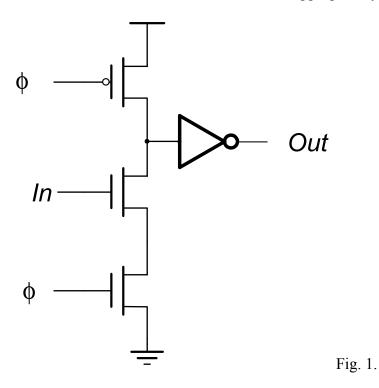

a) (4pts) Find the logical effort for a domino buffer from the figure. Assume that the static inverter PMOS/NMOS ratio is appropriately skewed.

b) (8pts) Calculate the optimal stage effort (product of the logical effort and fanout) for the domino buffer with a foot switch (as one shown in Fig.1).

(Hint: we calculated that the optimal effort for the static complementary CMOS stage is about 4. Recalculate this for the domino buffer that consists of a dynamic inverter and a skewed static inverter).

Optimal fanout =

#### **PROBLEM 3:** Arithmetic Circuits (10pts)

Consider an implementation of a bit-sliced 32-bit carry-lookahead adder implemented in static CMOS. The bit slice is 18 metal pitch, and the metal pitch is 1um. You can assume that the resistance of all metal layers is  $0.1\Omega/\Box$ . The table below shows the dependence of the intra-layer capacitance per unit length for the metal layer that is used for implementation of this carry wire.

| Spacing     | Min     | 1.5 * Min | 2 * Min | 2.5* Min | 3 * Min or more |

|-------------|---------|-----------|---------|----------|-----------------|

| Capacitance | 80aF/µm | 60aF/µm   | 50aF/µm | 45aF/µm  | 40aF/µm         |

- a) (2pts) How many bit slices does the longest carry wire cross in radix-2 implementation?

- b) (2pts) How many bit slices does the longest carry wire cross in radix-4 implementation?

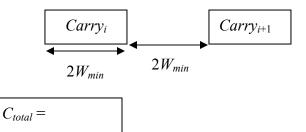

- c) (2pts) What is the worst-case coupling capacitance of the wire when all the carries are routed vertically with double-width, double-spaced pitch?

d) (2pts) How does this capacitance change if the wire pitch is doubled from the previous case, without changing the wire width?

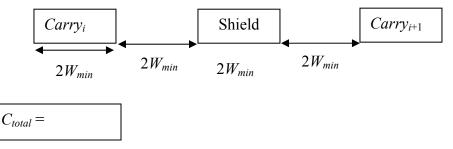

e) (2pts) If the shielding wires are introduced in the same layer as shown before, what is the worst-case coupling capacitance?

EECS 141: FALL2002 – MIDTERM 2

## **PROBLEM 4.** Power dissipation (6 pts).

Compute the probability of the energy consuming transitions of the output, *F* of the logic function  $F = \overline{A + B \cdot C}$ , implemented in standard static CMOS, if the input probabilities are p(A=1) = 0.2, p(B=1) = 0.5, p(C=1) = 0.1.