University of California College of Engineering Department of Electrical Engineering and Computer Sciences

B. Nikolić

Thursday, October 3, 2002 6:00-7:30pm

# EECS 141: FALL 2002-MIDTERM 1

For all problems, you can assume the following transistor parameters (unless otherwise mentioned): NMOS:  $V_{Tn} = 0.4, k'_n = 115 \mu A/V^2, V_{DSAT} = 0.6V, \lambda = 0, \gamma = 0.4 V^{1/2}, 2\Phi_F = -0.6V$ PMOS:  $V_{Tp} = -0.4V, k'_p = -30 \mu A/V^2, V_{DSAT} = -1V, \lambda = 0, \gamma = -0.4 V^{1/2}, 2\Phi_F = 0.6V$

|--|

| GRAD/UNDERGRAD |  |

|----------------|--|

|----------------|--|

- Problem 1: \_\_\_\_/ 12

- Problem 2: \_\_\_\_/ 20

- **Problem 3:** / 10

- Total: \_\_\_\_/ 42

### PROBLEM 1. (10 pts) MOS transistor as a switch

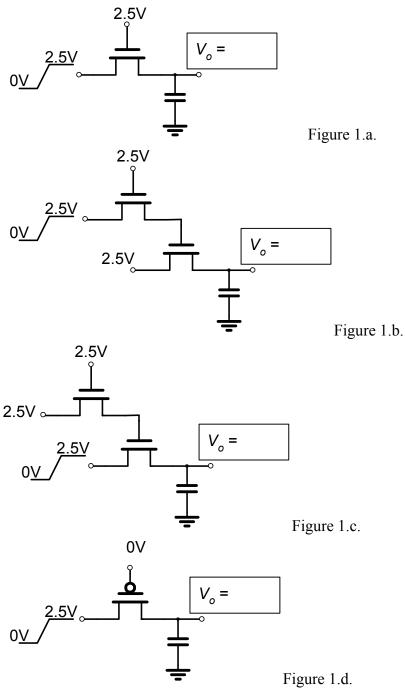

a) (4 pts) Find the final value of the voltage  $V_o$ , as a response to a LH transition at the input as shown in Figures 1.a – 1.d. Assume  $V_{TN} = |V_{TP}| = 0.5$ V. Assume that the capacitor is initially discharged, and ignore subthreshold conduction and body effect.

**b)** (2pts) When the output reaches its final value, a 2.5V to 0 step is applied to the input. Determine the energy consumed in the transistors from Figure 1.c. during the transition (in symbolic terms).

# $E_{1 \rightarrow 0} =$

c) (6pts) For Figure 1.d, Find the energy dissipated in the transistor during the first  $0 \rightarrow 1$ transition. Then, when the output reaches its final value, a 2.5V to 0 step is applied to the input, followed by the second 0 to 2.5V step. Find the energy dissipated in the transistor in the first  $1 \rightarrow 0$  transition, and the second  $0 \rightarrow 1$  transition (in symbolic terms).

First  $E_{1 \rightarrow 0} =$ First  $E_{0 \rightarrow 1} =$ Second  $E_{1 \rightarrow 0} =$

#### PROBLEM 2. (20pts) Transistor sizing.

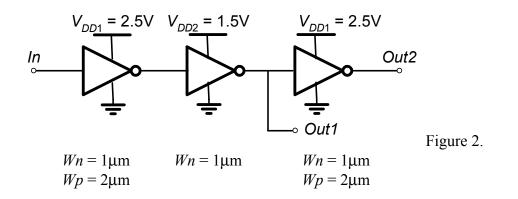

An inverter chain is shown in Figure 2. The first and the third inverter are supplied from  $V_{DD1} = 2.5$ V, while the second inverter is supplied from  $V_{DD2} = 1.5$ V. The input to the inverter chain swings between 0 and 2.5V. All transistors are minimum length, L = 0.25µm.

a) (8pts) If the width of the NMOS transistor in the second stage is  $Wn = 1\mu$ , find the size of the PMOS transistor, such that the second inverter exhibits the same LH and HL propagation delays (output *Out1*).

Wp =

**b)** (8pts) Determine the high and low output levels at the node *Out2*. Hint: You can make a reasonable assumption on the operating modes of transistors, but you have to prove that these assumptions are correct when you find the solution.

$V_{OH} =$  $V_{OL} =$

c) (4pts) How would you resize the third inverter to improve the noise margins?

## **3. CMOS Scaling (10pts)**

A microprocessor consumes 0.3 mW/MHz when fabricated using a  $0.13 \mu \text{m}$  process. The area of the processor is  $0.7 \text{ mm}^2$ . Assume a 200 MHz clock frequency, and 1.2 V power supply. Its leakage power is 0.1 mW. Assume short channel devices, but ignore second order effects like mobility degradation, series resistance, etc.

**a)** (5pts) If the supply voltage of the microprocessor scaled to 90 nm is reduced to 1.0 V, what will the area, frequency, power consumption, and power density be?

**b)** (5pts) If the threshold voltage in the 0.13  $\mu$ m process is 0.35V, what should be the threshold voltage in 90nm? Assuming 80mV/dec subthreshold slope, what would be the leakage power of the new processor?