| Name     |  |

|----------|--|

| T 100TTT |  |

| SID |  | 8.3 |

|-----|--|-----|

| 1. | [6] You purchased a power NMOSFET and want to verify                  |

|----|-----------------------------------------------------------------------|

|    | the DC parameters on the datasheet: $V_t$ , $\mu_n C_{ox}(W/L)$ , and |

|    | λ. Using two voltage sources and a current meter explain              |

|    | exactly what circuit setup you would use, what                        |

|    | measurements you would take, and what calculations you                |

|    | would do. Assume that the device is quadratic.                        |

| Prob. | Score |

|-------|-------|

| 1+2   | /10   |

| 3     | /12   |

| 4     | /10   |

| 5     | /11   |

| 6     | /13   |

| 7     | /12   |

| 8     | /12   |

| 9     | /12   |

| Total | /     |

sweep VGS, measure ID

Plot VID VS. VGS

Slope is VMnCox W

intercept is Vt

pick VGS VI Sweep VDS, necsure ID, plot ID VS VDS measure slope go Bag

V<sub>D</sub>s

2. [4] Later you bias a similar device with both the gate at 5V and the drain at 120V and the source grounded, and measure a drain current of 1A. Increasing the gate voltage to 6V increases the current to 2A. With the gate still at 6V, you have to decrease the drain voltage to 20V in order to get the current to drop back to 1A. Near these bias points,

a. What is the transconductance  $g_m$ ?  $g_2 = \frac{1A}{1V} = 15$

b. What is the output resistance  $r_0$ ?  $r_0 = \frac{100 \text{ V}}{1 \text{ A}} = 100 \Omega$

c. What is the channel length modulation parameter  $\lambda$ ?  $\lambda = \frac{1}{\sqrt{5}} = 1/100 \text{ V}$

d. What is the intrinsic gain?

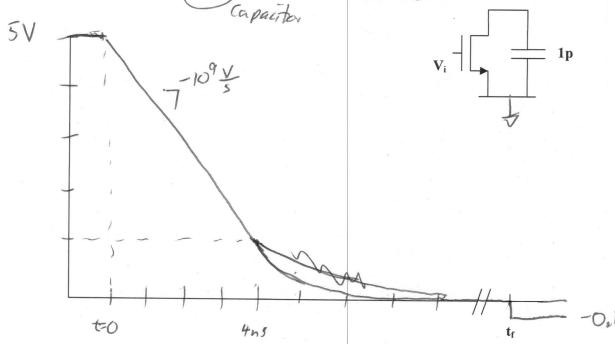

- 3. [12] At t=0, the input voltage  $V_i$  below transitions from 0 to 2V. The capacitor starts with an initial voltage of 5V.  $\mu_n C_{ox} = 200 \mu A/V^2$ ,  $V_t = 1V$ , W/L = 10. Assume  $\lambda = 0$ .

- a. [1] What is the initial current in the MOSFET immediately after t=0?

b. [1] What is the initial rate of change of the capacitor voltage?

c. [1] How long does it take the capacitor voltage to decrease to 1V?

d. [1] What is R<sub>on</sub> for the MOSFET in the triode region?

e. [2] How long does it take the charge on the capacitor to decrease from 0.1V to 0.1 mV?

Out to 0.1 mV? 0.1 mV = 3.5 m/s

- f. [2] If  $C_{gd}$  of the MOSFET is 0.1 pF, and at  $t=t_f$  that is long compared to the times above the input voltage slowly transitions back to 0, what is the charge injected and the final voltage on the capacitor?  $C_{gd} V_{t} = (0.1 \text{ pF})(1.0) = 0.1 \text{ pC}$

- g. [4] Carefully sketch the output voltage versus time, labeling each axis.

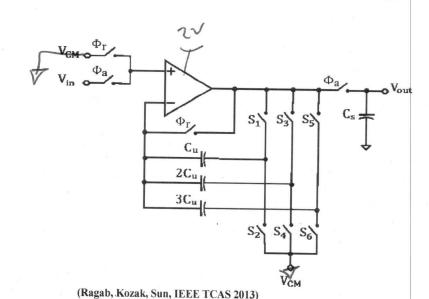

- 4. [10] In the circuit below, assume that  $V_{CM} = 0$ , and the op-amp is running from a single-sided 2V supply. Assume that  $\Phi_{r}$  and  $\Phi_{a}$  are non-overlapping clocks.

- a. [1] during  $\Phi_r$ , which switches should be closed to ensure that there is no charge on the capacitors, and the op-amp is working normally in unity gain feedback?

b. [2] in Φ<sub>a</sub> what is the feedback factor if switches S1, S4, and S6 are closed (and 2, 3, and 5 remain open)? What is the gain?

c. [1] If a settling accuracy of 0.1% is required with this switch setting, what is the minimum DC gain necessary for the op-amp?

d. [2] With this settling accuracy requirement, and  $\Phi_a$  phase duration of  $1\mu s$ , what is the minimum open-loop unity gain bandwidth of the op-amp?

e. [2] List all possible gains, if different switch settings are used.

$$w = \frac{1}{2} = \frac{7mred}{5}$$

$$w = \frac{1}{5} = \frac{7mred}{5}$$

f. [2] What op-amp topologies would work for this circuit? (list all viable combinations of simple single stage, two stage, FC, FC two stage, and NMOS or PMOS input)

PMOS MPV FC 2 stage

F Gu

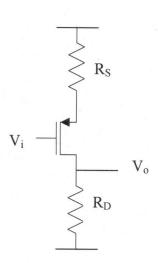

- 5. [11] For the amplifier in the figure to the right

- a. [2] Draw the small signal model labeling the small signal variables  $v_i,\,v_o,\,i_o,\,v_s$

b. [1] Write an expression for  $G_m$  as the ratio of two small signal parameters while a third is held equal to zero.

- c. [1] Given the conditions above for the calculation of  $G_m$ , write  $v_s$  in terms of  $i_o$   $V_5 = i_s R_5$

- d. [2] Given the conditions above for the calculation of  $G_m$ , write KCL @  $v_o$  and solve for  $G_m$ .

$$i_{o} = g_{m} v_{ss} + \frac{1}{r_{o}} (v_{o} - v_{s})$$

$$= g_{n} v_{i} + (g_{m} + \frac{1}{r_{o}})(-v_{s})$$

$$i_{o} \left[ 1 + (g_{m} + \frac{1}{r_{o}})R_{s} \right] = g_{m} v_{i}$$

e. [3] Find the approximate value for  $G_m$  for each of three different values of  $R_S$ : much less than  $1/g_m$ , equal to  $1/g_m$ , and much greater than  $1/g_m$ .

$$G_{m} = \begin{cases} G_{m} & R_{s} \leq \frac{1}{5m} \\ G_{m} = \frac{1}{5m} \\ R_{s} = \frac{1}{5m} \\ R_{s} > \frac{1}{5m} \end{cases}$$

f. [1] Write the full expression for R<sub>o</sub>. (you don't need to derive it)

g. [1] If  $R_S$  is much greater than  $1/g_m$ , and  $R_D=2R_S$ , roughly what is the gain?

- 6. [13] You have designed a two stage Miller-compensated op-amp with a phase margin of 45 degrees in unity gain feedback. The load capacitance is more than 10 times bigger than any other capacitor in the circuit. You have removed the RHP zero from the compensation capacitor.

- a. [5] Carefully sketch a Bode plot of the open-loop gain. Assume that the DC gain is roughly 1000.

b. [2] If you increase the load capacitance by a factor of 10, what happens to the phase margin? Unity gain frequency?

c. [2] If instead you increase the compensation capacitor by 10x, what happens to the phase margin and unity gain frequency?

d. [2] If you increase both the load capacitance and the compensation capacitor by 10x, what happens to the phase margin and unity gain frequency?

e. [2] If you have a single-stage folded cascode op-amp with a unity-gain phase margin of 45 degrees and you increase the load capacitance by 10x, what happens to the phase margin and unity gain frequency?

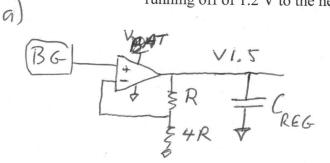

- 7. [12] In your project, you are having some trouble with leakage on the ADC V<sub>ref</sub>LD switch. You decide that the best solution is to generate another regulated voltage, this one at 1.5V, to use for the gate and body of that PMOS switch.

- a. [4] Using your bandgap reference of 1.2V, sketch the complete regulator circuit. Start at a high level, with an op-amp symbol, some resistors, etc.

- b. [4] Show the schematic for your op-amp, including what overdrive voltages you would pick. You may assume that op-amp internal bias voltages are generated elsewhere.

- c. [2] Discuss the stability of the loop, and how you would guarantee it.

- d. [2] Also show the circuit that you would use to convert the original LD signal running off of 1.2 V to the new LD<sub>1.5</sub> signal at 1.5V.

b) Use 2 stope nones iput FC. 2nd stope would have Vov= 100pl So would first stage. Need inpit compare near top vail, extent suring new top rail (100mV) c) need to add a componentes carerdon, for Miller comp.

Size CREG to set low ripple on inverter switching. Prolably very shell. So 2nd store will have high fing, pole. Want need to compensate much.

Minimum sized devices will be fine, sain fairly low.

6 130/65 1 20/65

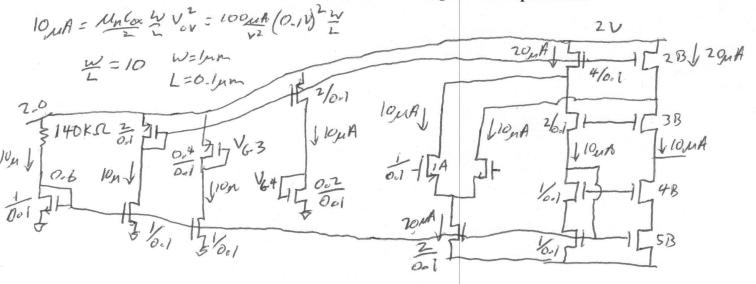

- 8. [12] Design an NMOS-input folded cascode op-amp with the following specs:

- a. 20uA tail current

- b. able to source or sink 20uA to/from the load when slewing

- c. output swing to within 200mV of the rails

- d. minimum channel length

Process specs  $\mu_n C_{ox} = 200 \mu A/V^2$ ,  $\mu_p C_{ox} = 100 \mu A/V^2$ ,  $\lambda = L_{min}/(1V*L)$ ,  $-V_{tp} = V_{tn} = 0.5V$ ,  $V_{DD} = 2V$ ,  $L_{min} = 0.1 um$ ,  $C_{ox} = 5 f F / um^2$ ,  $C'_{ol} = 0.5 f F / um$ . You may use 1 resistor in your design.

Draw the schematic including bias circuits, label the device size of each transistor or transistor pair and the bias current flowing in each leg. Calculate the gain, the input capacitance, and the bandwidth when driving a 100fF capacitance.

$$g_{m1} = \frac{20_{uf}}{0_{o}l_{m}V} = 200_{us}$$

$$f_{o} = \frac{1}{(1)(10_{u})} = 100 \text{ KJZ}$$

$$g_{m} f_{o} = 20$$

$$A_{V} = \frac{1}{4} (g_{m} f_{o})^{2} = 100$$

$$W_{u} = \frac{200_{us}}{100 \text{ ff}} = 2 \times 10^{9} \text{ red}$$

$$C_{SB} = \frac{2}{3}O_{0.5}ff \approx 0.3fF$$

$$C_{Sd} = 0.5fF$$

$$C_{in} = C_{SS} + (i-A)C_{Sd}$$

$$= 0.3ff + 5ff$$

$$\approx 5fF$$

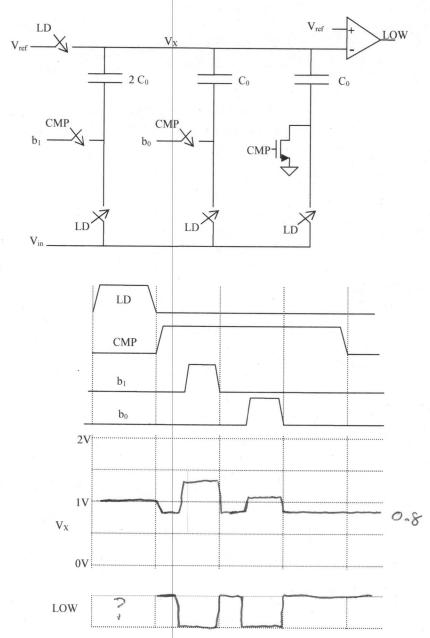

- 9. [12] In the following 2 bit ADC circuit, LD and CMP are non-overlapping clocks. Assume that the RC time constants are fast compared to the time scale below.

- a. [10] Assuming  $V_{in}$ =0.2V, carefully sketch the waveforms on Vx and LOW on the graph provided below.  $V_{ref}$ =1V. b1 and b0 are either 0 or 1V.

- b. [1] What binary value should the SAR report when  $V_{in}=0.2$ ?

00

c. [1] If the comparator is implemented as an op-amp running from a supply voltage of  $V_{\text{ref}}$ , what topologies can be used?

NMOS impto FC.