# University of California at Berkeley College of Engineering Dept. of Electrical Engineering and Computer Sciences

## EE 105 Midterm 1

## Spring 2006 Prof. Ming C. Wu

| Problem | Points | Score |

|---------|--------|-------|

| 1       | 20     |       |

| 2       | 40     |       |

| 3       | 10     |       |

| 4       | 10     |       |

| 5       | 20     |       |

| Total   | 100    |       |

- You may use a calculator

- Show all your work and reasoning on the exam in order to receive full or partial credit.

- Write your answer in the designated page for each problem. If you need more space, use the "Additional Space" at the end.

- Please put a box around the final answer of each sub-problem

- Time: 90 minutes

#### Please use the following parameters for all problems unless specified otherwise:

$$\Phi_{n+} = 550 \text{ mV}, \ \Phi_{p+} = -550 \text{mV}, \ V_{th} = 26 \text{mV}$$

$\epsilon_{Si} = 11.7, \ \epsilon_{SiO2} = 3.9, \ \epsilon_0 = 8.854 \text{ x } 10^{-14} \text{ F/cm},$

$Q = 1.6 \text{ x } 10_{-19} \text{ C}, \ n_i = 10^{10} \text{ cm}^{-3}$

- 1. Consider a silicon PN junction diode with an N-doping concentration of 10<sup>16</sup> cm<sup>-3</sup> and a P-doping concentration of 10<sup>18</sup> cm<sup>-3</sup>. Their cross-sectional area of the diode is 100 um<sup>2</sup>. Assume the reverse saturation current of the diode is 10<sup>-14</sup> Amp. The diode is forward biased at 0.7V.

- a) [10pt] Find the dynamic resistance at this bias.

- b) [10pt] Find the depletion capacitance at this bias.

- 2. Consider a MOS capacitor with a P+ polysilicon gate and an N-doped substrate with a doping concentration of 10<sup>16</sup> cm<sup>-3</sup>. The thickness of the oxide is 230nm.

- a) [10pt] Find the threshold voltage.

- b) [10pt] Which mode is the MOS capacitor in when its gate is biased at 1V?

- c) [10pt] What is the maximum capacitance per unit area?

- d) [10pt] What is the minimum capacitance pr unit area?

- 3. [10pt] For the MOS capacitor in Problem (2), plot the charge density distribution as a function of position when the gate is biased at –2V. Please be as quantitative as possible. Show the positions of all charges, and show the magnitude and polarity of the charges.

- 4. [10pt] If the P+ gate of the MOS capacitor in Problem (2) is replaced by a metal whose electrostatic potential is 0V. What is the threshold boltage of the new MOS capacitor?

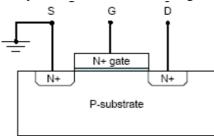

- 5. Consider an N-MOSFET with an N+ polysilicon gate on P-type substrate ( $N_a = 10^{17} \text{ cm}^{-3}$ ). The source is grounded, and the drain is biased at 5V. The transistor has a gate length of 1 um, and a width of 10 um. The thickness of the gate oxide is 10 nm. For simplicity, assume the channel-length modulation parameter  $\lambda = 0$ .

- a) [10pt] At what gate voltage does the transistor turn on, i.e., start to have significant current flowing between source and drain?

- b) [10pt] Find the drain current when the gate is biased at 2V.

#### **Some equations**

Mass-action law  $n \times p = n_i^2(T)$

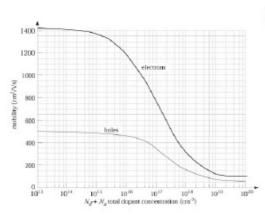

Resistivity:  $\rho_n = \frac{1}{\sigma_n} = \frac{1}{q\mu_n N_{d eff}}$

Resistance:

$$R = \frac{\rho L}{Wt} = \left(\frac{\rho}{t}\right)\left(\frac{L}{W}\right) = R_{sq}\left(\frac{L}{W}\right)$$

Total current (e):  $J = J_{drift} + J_{diff} = q\mu_n nE + qD_n \frac{dn}{dx}$

Gauss's law:

$$\oint E \cdot dS = \frac{Q}{\epsilon}$$

$Q = CV$   $E = -\frac{d\phi}{dx}$

Depletion layer:

$$X_{d0} = x_{p0} + x_{n0} = \sqrt{\frac{2\varepsilon_{S}\varphi_{bi}}{q}\left(\frac{1}{N_{a}} + \frac{1}{N_{d}}\right)} \qquad X_{d}(V_{D}) = X_{d0}\sqrt{1 - \frac{V_{D}}{\varphi_{bi}}}$$

pn depletion layer capacitance:

$$C_{j} = \frac{qN_{a}x_{p0}}{2\varphi_{bi}\sqrt{1 - \frac{V_{D}}{\varphi_{bi}}}} = \frac{C_{j0}}{\sqrt{1 - \frac{V_{D}}{\varphi_{bi}}}}$$

pn diffusion current

$$J^{diff} = qn_{i}^{2}\left(\frac{D_{p}}{N_{d}W_{n}} + \frac{D_{n}}{N_{a}W_{p}}\right)\left(e^{\frac{qv_{D}}{kT}} - 1\right)i_{D} = I_{S}\left(e^{\frac{qv_{D}}{kT}} - 1\right)$$

Diffusion capacitance:  $C_d = \frac{1}{2} \frac{q I_D}{kT} \tau$

Threshold voltage (NMOS)

$$\begin{split} V_{Tn} &= V_{FB} - 2\varphi_p + \frac{1}{C_{ox}} \sqrt{2q\varepsilon_s N_a \left(-2\varphi_p\right)} \\ V_{Tn} &= V_{Tn0} + \gamma \left(\sqrt{V_{SB} - 2\varphi_p} - \sqrt{-2\varphi_p}\right) \end{split}$$

$$\varphi_p = -\frac{kT}{q} \ln \frac{N_a}{n_i}$$

NMOS equations:

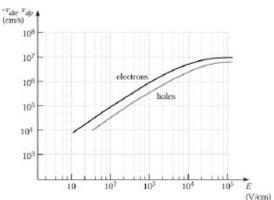

$$\begin{split} I_D &= 0, \quad V_{GS} < V_{Tn} \\ i_D &= \frac{W}{L} \mu C_{ox} \left( v_{GS} - V_{Tn} - \frac{v_{DS}}{2} \right) v_{DS} \left( 1 + \lambda V_{DS} \right), \quad V_{GS} > V_{Tn}, \, V_{DS} < V_{GS} - V_{Tn} \\ i_D &= \frac{W}{L} \frac{\mu C_{ox}}{2} \left( v_{GS} - V_{Tn} \right)^2 \left( 1 + \lambda V_{DS} \right), \quad V_{GS} > V_{Tn}, \, V_{DS} > V_{GS} - V_{Tn} \end{split}$$

MOS capacitances in saturation  $C_{gs} = (2/3)WLC_{ox} + C_{ov}$   $C_{ov} = L_DWC_{ox}$

MOS signal parameters:

$$g_{m} = \frac{\partial i_{D}}{\partial v_{GS}}\bigg|_{V_{GS}, V_{DS}} = \mu C_{ox} \frac{W}{L} (V_{GS} - V_{Tn})(1 + \lambda V_{DS}) \approx \mu C_{ox} \frac{W}{L} (V_{GS} - V_{Tn})$$

$$r_{o} = \left(\frac{\partial i_{D}}{\partial v_{DS}}\Big|_{V_{GS}, V_{DS}}\right)^{-1} \approx \frac{1}{\lambda I_{DS}}$$

$$g_{mb} = \frac{\partial i_D}{\partial v_{BS}}\bigg|_Q = \frac{\gamma g_m}{2\sqrt{-V_{BS}-2\varphi_p}}$$