Ground Rules:

- Close book; one 8.5x11 crib sheet (both sides)

- Do all work on exam pages

- Default bipolar transistor parameters:

- ♦*npn*: β<sub>n</sub>=100, V<sub>An</sub>=50 V, V<sub>CE-sat</sub>=0.2 V

- $pnp: \beta_p=50, V_{Ap}=25 \text{ V}, V_{EC-sat}=0.2 \text{ V}$

- Default MOS transistor parameters: note LAMBDA depends on L!

- NMOS: MU<sub>n</sub> C<sub>ox</sub>=100e-6 A/V<sup>2</sup>, LAMBDA<sub>n</sub>=[0.1/L] V<sup>-1</sup> (L in micrometers) V<sub>Tp</sub>=1 V • PMOS: MU<sub>p</sub> C<sub>ox</sub>=50e-6 A/V<sup>2</sup>, LAMBDA<sub>p</sub>=[0.1/L] V<sup>-1</sup> (L in micrometers) V<sub>Tp</sub>=-1 V

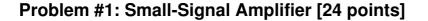

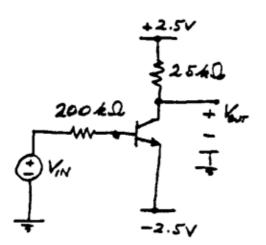

a) [4 pts.] What is width of transistor  $M_2$  such that the DC output voltage  $V_{out}=0$  V for  $V_{IN}=0$  V. Given: the length of  $M_2$  is  $L_2=2e-6$  m.

b) [4 pts.] What is the numerical value of the input resistance  $R_{in}$  of this amplifier? Your answer should be correct to within +/- 5%.

If you couldn't solve (a) you can assume for this part that  $W_2=25e-6$  m. Of course, this isn't the correct answer to part (a).

c) [4 pts.] What is the numerical value of the output resistance  $R_{out}$  of this amplifier? Your answer should be correct to within +/- 5%.

If you couldn't solve (a) you can assume for this part that  $W_2=25e-6$  m. Of course, this isn't the correct answer to part (a).

d) [6 pts.] What is the numerical value of the overall voltage gain  $v_{out}/v_s$ , with  $R_s=100$  kilo-ohms and  $R_L=20$  kilo-ohms? Your answer should be correct to within +/- 5%.

Again, If you couldn't solve (a) you can assume for this part that  $W_2=25e-6$  m. Of course, this isn't the correct answer to part (a).

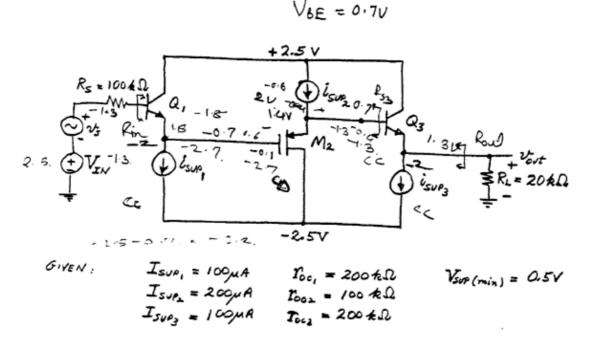

e) [6 pts.] Sketch the transfer curve V<sub>OUT</sub> versus V<sub>IN</sub> for -2.5 <= V<sub>IN</sub> <= +2.5 V on the graph below. For this part,  $R_L$  is infinity and  $R_S$ =0 V.

Hint: you should note that the current supplies each require at least V<sub>SUP(min)</sub>=0.5 V in order to function.

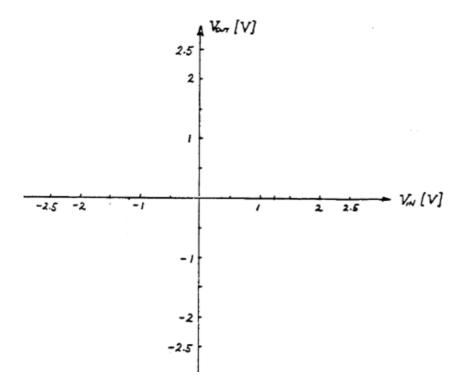

## Problem #2: Digital Logic Gate [14 points]

## EE 105, Midterm 2, Fall 1996

a) [2 pts.] What is the logic operation performed by the above circuit? In other words, what is the logical expression for Q in terms of the three inputs A, B and C?

b) [4 pts.] The graphs below plot the voltage waveforms over an interval of 35 microseconds. Fill in the output voltage waveform  $v_Q(t)$  over 0 -=> 35e-6 s. Note that the rise and fall times are essentiall zero on this time scale.

c) [4 pts.] Find the numerical value of the **best case** low-to-high propagation delay (t<sub>PLH</sub>) for this logic gate.

d) [4 pts.] Find the width of the n-channel transistor such that the high-to-low propagation delay ( $t_{PLH}$ ) is equal to your answer for part c). If you couldn't answer part c) you can assume for this part that  $t_{PLH (best)} = 1$  ns = 10<sup>-9</sup>s.

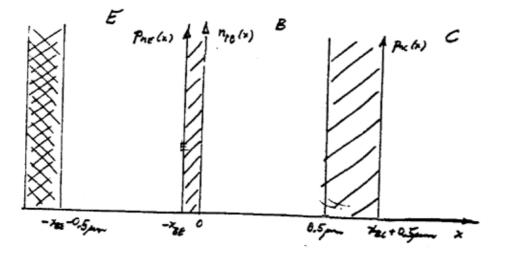

## Problem #3: Bipolar Transistor Physics [12 points]

NOTE: The default npn transistors do not apply for this problem!

GIVEN:  $N_{dE}=2x10^{18} \text{ cm}^{-3}$   $N_{dB}=10^{17} \text{ cm}^{-3}$

Problem #2: Digital Logic Gate [14 points]

N<sub>dC</sub>=1016 cm-3

The base and emitter widths are  $W_B=W_E=0.5$  micrometers. The electron diffusion coefficient in the base is  $D_{nB}=10 \text{ cm}^2/\text{s}$  and the hole diffusion coefficient in the emitter is  $D_{pE}=5 \text{ cm}^2/\text{s}$ .

a) [3 pts.] Qualitatively sketch the minority carrier concentrations in the emitter, base and collector on the graph below, assuming that the transistor is biased in the forward active region.

b) [3 pts.] For V<sub>OUT</sub>=0 V what is the numerical value of the minority electron concentration at x=0,  $n_{pB}(0)$ ? You can assume that the transistor is biased in the forward active region.

c) [3 pts.] What is the numerical value of the base current I<sub>B</sub> for the bias condition in part b)? If you couldn't solve b) assume for this part that  $n_{pB}(0) = 10^{15}$  cm<sup>-3</sup> -- not the correct answer to b), of course. d) [3 pts.] What is the numerical value of V<sub>IN</sub> in order that the transistor is biased in the forward active region with V<sub>OUT</sub>=0 V?

Notes: You cannot assume that  $V_{BE}=0.7$  V for this part. If you couldn't solve parts b) and c) you can assume that  $n_{pB}(0)=10^{15}$  cm<sup>-3</sup> and that  $I_{B}=4$  micro-amps. Neither of these answers are correct, of course.

## Answers!

Posted by HKN (Electrical Engineering and Computer Science Honor Society) University of California at Berkeley If you have any questions about these online exams please contact <u>examfile@hkn.eecs.berkeley.edu.</u>