# University of California, Berkeley - College of Engineering

Department of Electrical Engineering and Computer Sciences

Spring 2008

Instructor: Dr. Dan Garcia

2008-05-19

# ⊗CS61C Final ☺

After the exam, indicate on the line above where you fall in the emotion spectrum between "sad" & "smiley"...

| Last Name                                                                                                                   | Answer Key |     |      |      |      |      |      |   |      |     |      |    |     |

|-----------------------------------------------------------------------------------------------------------------------------|------------|-----|------|------|------|------|------|---|------|-----|------|----|-----|

| First Name                                                                                                                  |            |     |      |      |      |      |      |   |      |     |      |    |     |

| Student ID Number                                                                                                           |            |     |      |      |      |      |      |   |      |     |      |    |     |

| Login                                                                                                                       | cs         | 610 | 2-   |      |      |      |      |   |      |     |      |    |     |

| Login First Letter (please circle)                                                                                          | a          | b   | С    | d    | е    | f    | g    | h | i    | j   | k    | 1  | m   |

| Login Second Letter (please circle)                                                                                         | а          | b   | С    | d    | е    | f    | g    | h | i    | j   | k    | 1  | m   |

|                                                                                                                             | n          | 0   | р    | q    | r    | s    | t    | u | v    | W   | х    | У  | z   |

| The name of your <b>SECTION</b> TA (please circle)                                                                          | B          | en  | Bria | in ( | Case | ey l | Dave | K | eatc | n I | Matt | On | nar |

| Name of the person to your Left                                                                                             |            |     |      |      |      |      |      |   |      |     |      |    |     |

| Name of the person to your Right                                                                                            |            |     |      |      |      |      |      |   |      |     |      |    |     |

| All the work is my own. I had no prior knowledge of the exam<br>contents nor will I share the contents with others in CS61C |            |     |      |      |      |      |      |   |      |     |      |    |     |

| who have not taken it yet. (please sign)                                                                                    |            |     |      |      |      |      |      |   |      |     |      |    |     |

## **Instructions (Read Me!)**

- This booklet contains 9 numbered pages including the cover page.

Put all answers on these pages; don't hand in any stray pieces of paper.

- Please turn off all pagers, cell phones & beepers. Remove all hats & headphones. Place your backpacks, laptops and jackets at the front. Sit in *every other* seat. Nothing may be placed in the "no fly zone" spare seat/desk between students.

- You have 180 minutes to complete this exam. The exam is closed book, no computers, PDAs or calculators. You may use two pages (US Letter, front and back) of notes and the green sheet.

- There may be partial credit for incomplete answers; write as much of the solution as you can. We will deduct

points if your solution is far more complicated than necessary. When we provide a blank, please fit your answer

within the space provided. "IEC format" refers to the mebi, tebi, etc prefixes.

- You must complete ALL THE QUESTIONS, regardless of your score on the midterm. Clobbering only works from the Final to the Midterm, not vice versa. You have 3 hours... relax.

| Question | M1 | M2 | М3 | Ms | <b>F1</b> | F2 | F3 | <b>F4</b> | Fs  | Total |

|----------|----|----|----|----|-----------|----|----|-----------|-----|-------|

| Minutes  | 20 | 20 | 20 | 60 | 24        | 30 | 24 | 42        | 120 | 180   |

| Points   | 10 | 10 | 10 | 30 | 18        | 24 | 18 | 30        | 90  | 120   |

| Score    | 10 | 10 | 10 | 30 | 18        | 24 | 18 | 30        | 90  | 120   |

Confessional:

Name:

```

Answer Key Login: cs61c-____

```

## M1) Hey buddy, can you run these instructions for me? Thanks! (10 pts, 20 min)

Consider the following *non-delayed branch* MIPS function foo:

| foo<br>a) What does the following function call (in C) return?32<br>foo(-1, 0x30880001, 0x00481020, 0x00042042);    | <pre>b: li \$v0,0     la \$t9,loop     sw \$a1,0(\$t9)     sw \$a2,4(\$t9)     sw \$a3,8(\$t9)</pre> |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| <pre>\$a0 = -1  # 0xFFFFFFF andi  rs=a0 rt=t0 1 001100 00100 01000 0000000000000 0011 0000 1000 1000 00000000</pre> | pp: nop<br>nop<br>nop<br>bne \$a0,\$0,loop<br>jr \$ra                                                |

| add R[rd]=R[rs]+R[rt]<br>R  rs=v0 rt=t0 rd=v0 sha=0 add<br>000000 00010 01000 00010 00000 100000<br>0000 0000       |                                                                                                      |

| <pre>srl R[Rd]=R[rt]&gt;&gt;shamt R</pre>                                                                           |                                                                                                      |

| The small loop simply counts the 1s in \$a0.                                                                        |                                                                                                      |

b) You can probably see how foo could pose a security threat if misused. For the good of humanity, we must seal its functionality forever, and render it harmless. That is, you're going to call it once with a special set of arguments for \$a0-\$a3 (list these below in human-readable form ... not as numbers!) so that every future call to foo always just returns \$a0 regardless of the value of \$a1-\$a3. Oh, and the call to foo with the arguments below should cause it (this time only) to return 0 to signal success that it has been "neutralized".

```

add $v0, $a0, $0 # /or/ addi $v0,$a0,0

$a0:

sw $a0,-20($t9) #offset can be 20,16 or 12

$a1:

sw $a3,-16($t9) # offset can be 16,12 or 10 (as long as its less than previous)

$a2:

jr $ra # NOT beg $0,$0,7 (unconditional br to existing jr doesn't work 1<sup>st</sup> time)

```

```

$a3:

```

## M2) This SEEEEMMMs hard! Yeah, but you're biased! (10 pts, 20 mins)

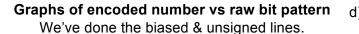

For this entire question, we only have a byte and consider different numeric encodings. Let's compare a floating point SEEEEMMM (1 Sign bit, 4 Exponent bits, 3 Mantissa bits) encoding with a biased encoding (the one we use to store the exponent in a 32-bit float) and an unsigned number. Given a raw bit pattern (in hex), we can ask each encoding what number it means. E.g., the raw bit pattern OXFF is a NaN for SEEEEMMM, but 128 for the biased encoding. One could plot the raw bit pattern vs. the number each encoding represents; if the result is not a number (e.g.,  $\infty$  or NaN), we just don't plot it. We've already plotted the biased and unsigned lines. Sketch the SEEEMMM curve and answer the following questions. Your sketch can be quite rough. I.e., there's no need to calculate exact points or intersections, as long as the number of intersections is correct & it has the right general shape.

- a) How many times does the SEEEEMMM curve intersect the unsigned line? 2

- b) How many times does the SEEEEMMM curve intersect the biased line? 0

d) Every region where the SEEEEMMM curve has a slope of 1 (i.e., is it equal to the slope of the two lines drawn), write down the ranges of the raw bit patterns and the difference from the unsigned line. E.g., (these are just for illustration, they're wrong) "from 0x3F to 0xEA it's 99 more than unsigned, and from 0xF1 to 0xF5 it's 10 less than it." Fill in the table below; you may not need all rows.

| From | То   | SEEEEMMM<br>compared to<br>unsigned line |

|------|------|------------------------------------------|

| 0x3F | 0xEA | 99 more                                  |

| 0xF1 | 0xF5 | 10 less                                  |

| 0x50 | 0x58 | 72 less                                  |

|      |      |                                          |

| I    |      |                                          |

| I    |      |                                          |

There's only one region; the slope slowly increases (from near 0 to way above 1) from  $0x00 \rightarrow 0x77$  (last Exp for inf/NaN) and slowly decreases (from near -0 to way below -1) from  $0x80 \rightarrow 0xF7$  (last Exp for inf/NaN). See curve. There are 4 E bits, so the bias is -7. The slope=1 when BitPattern+1 increments the float encoded # by one also. Float is  $1.MMM * 2^{E-bias}$ , and we want the LSB M to be a ones (i.e., Ob1MMM.O), then E-bias = 3, or E=10. The range is Ob1000 through to the next exponent, meaning M has all values Ob000 through Ob111 and even one more to Ob000 again. Summing up, the float encoded # is 0b1000 (8) through 0b10000 (16). For 8, the bit pattern is S=0 (positive), E=0b1010 (10) and M=0b000 (0), which is  $0|1010|000 \rightarrow 0x50$  through the next exponent (11), 0 | 1011 | 000 → 0x58. The SEEEEMMM value for 0x50 is 8, and since the unsigned value of 0x50 is 5\*16=80, we're 72 less.

## M3) Memories, like the smile we left behind... (10 pts, 20 mins)

a) Here is code and output for a small program, called memtest, run on an unknown machine with an unknown architecture.

What are two possible reasons the program didn't print out 1?

```

main() {

char *p = (char *) malloc (1);

char *q = (char *) malloc (1);

printf("%u\n", (unsigned int) q - (unsigned int) p);

}

unix% ./memtest

16

```

Three possible answers: (1) Could be slab allocated (smallest slab = 16 bytes)

(2) Freelist could have header to keep track of bookkeeping

(3) Finally, it could be that the system was quadword aligned (as Macs are)

00

b) Consider the heap pictured below. The first 8 bytes are reserved for the buddy system. The heap is filled left to right when more than one slot can satisfy a request. Any free buddy pairs are consolidated immediately when possible. For the series of memory requests below, fill in the heap snapshot after every 2<sup>nd</sup> line. Be sure to label your allocated space and the block boundaries, as is shown in the initial heap.

| 1      | C = malloc(1);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              | <──    |   | — I | Budo | dv S   | syster | n — |        | -> <  |        |         | - Re    | st of | Heap |    | $\rightarrow$        |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|---|-----|------|--------|--------|-----|--------|-------|--------|---------|---------|-------|------|----|----------------------|

| 2      | free(B);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              | o<br>I | 1 | 2   | 3    | 4<br>: | 5      | 6   | 7<br>; | 8<br> | 9<br>: | 10<br>: | 11<br>; | 12    | 13   | 14 |                      |

| 3<br>4 | <pre>D = malloc(2); free(A);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Initial Heap |        |   | В   | A    |        |        |     |        |       |        | -       |         |       |      |    | $\overline{\langle}$ |

| -      | and the second se | After Line 2 |        |   | -   |      |        |        |     |        |       |        |         |         |       |      |    | $\left\{ \right\}$   |

| 5<br>6 | E = malloc(3);<br>F = malloc(2);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | After Line 4 |        |   |     |      |        |        |     |        |       |        |         |         |       |      |    | 4                    |

| 7      | <pre>free(D);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | After Line 6 | L      |   |     |      |        |        |     |        |       |        |         |         |       |      |    |                      |

| 8      | G = malloc(3);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | After Line 8 | L      |   | -   | -    | -      |        |     |        |       |        |         |         |       | -    |    | 2                    |

For the following two questions, we are counting *the number of different instructions* (add, sub, ...), not including the arguments they could accept. E.g., add \$t0,\$t0,\$t0 and add \$s1,\$s2,\$s3 are only counted as one, add.

c) How many unique TAL MIPS instructions *could* (not do) we have? \_\_\_\_\_127\_\_\_\_\_

d) How many unique MAL MIPS instructions could (not do) we have?

| e) Fill the table with ALL the choices that<br>fit. Some may be blank, and the letters<br>may be used more than once. | Consumes<br>(input/uses) | Creates/Causes<br>(output/side-effects) |                                               |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------|-----------------------------------------------|

| 1. Slab Allocator                                                                                                     | G                        | F                                       | A. Executable<br>Bo files                     |

| 2. Assembler                                                                                                          | I                        | B, D, H                                 | C. Root Set<br>D. Relocation Table            |

| 3. Linker                                                                                                             | B, D, H, K               | A                                       | E. C Source Code<br>F. Internal Fragmentation |

| 4. Compiler                                                                                                           | Е                        | I                                       | G. Allocation Requests                        |

| 5. Reference Counting                                                                                                 | G, C                     | М                                       | H. Symbol Table<br>I. MAL                     |

| 6. Copying                                                                                                            | G, J, C                  |                                         | J. Half the Heap<br>K. Library Files          |

| 7. Mark and Sweep                                                                                                     | G, C                     | maybe L                                 | L. External Fragmentation<br>M. Memory Leak   |

## Name: \_\_\_\_\_\_Answer Key Login: cs61c-\_\_\_\_\_ F1) How many CS majors to change a lightbulb? None, that's HW! (18 pts, 24 mins)

Questions (a), (b), (c) and (d) are independent.

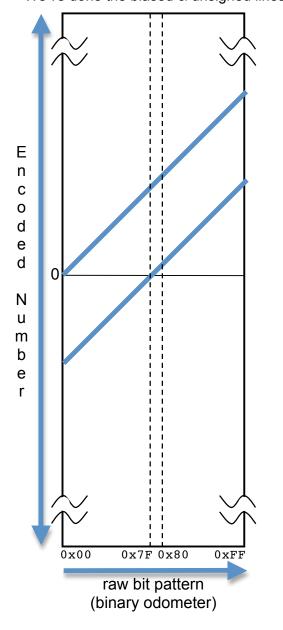

a) You are an intern at a massive hardware firm. Your first task is to design an "odd counter" circuit that receives a single bit input every cycle and outputs a single bit every cycle. <u>It outputs a 1 *if and only if* it has seen an</u> <u>odd number of ones AND an odd number of zeros.</u> It starts in a state where it has seen an even number of ones and an even number of zeros (remember, zero is an even number). As an example,

| the input:               | I: | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

|--------------------------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| will produce the output: | 0: | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

Complete the FSM diagram below. The names of the states are arbitrary, but use S00 is the start state. Fill in the truth table on the right. The previous state is encoded in (P1,P0), the next state is encoded in (N1,N0), and the output is encoded as 0. Make sure to indicate the value of the *output* on your state.

|    | _  |   |   |    | _  |

|----|----|---|---|----|----|

| Ρ1 | Р0 | I | 0 | N1 | NO |

| 0  | 0  | 0 | 0 | 0  | 1  |

| 0  | 0  | 1 | 0 | 1  | 0  |

| 0  | 1  | 0 | 0 | 0  | 0  |

| 0  | 1  | 1 | 1 | 1  | 1  |

| 1  | 0  | 0 | 1 | 1  | 1  |

| 1  | 0  | 1 | 0 | 0  | 0  |

| 1  | 1  | 0 | 0 | 1  | 0  |

| 1  | 1  | 1 | 0 | 0  | 1  |

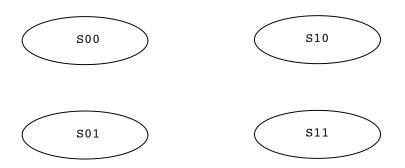

b) Rebuild this circuit with the **fewest** gates in the box to the right, using **ONLY** AND, OR and NOT gates.

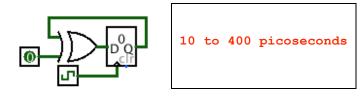

c) Finally, your boss wants you to choose an XOR gate for the circuit to the right: The clock speed is 2Ghz, the setup, hold, and clock-to-q times of the register are 40, 70, and 60 picoseconds (10<sup>-12</sup> s) respectively. What range of XOR gate delays is acceptable?

E.g., "at least W ps", "at most X ps", or "Y to Z ps".

d) You're asked to create all the unique 3-to-2 circuits (i.e., 3 inputs: 12, 11, 10 and 2 outputs), with one minor catch. Your circuit must ignore the value of 11 if the value of 12 is 1. How many different circuits will you have to make? Use IEC terminology, like 128 mebicircuits, 512 tebicircuits, etc.

#### Answer Key Login: cs61c-

## F2) You're using circular linked list reasoning (24 pts, 30 mins)

You have a 32-bit MIPS system with...

- 1 MiB of RAM (max)

- Virtual Memory with P-word pages (P is a power of 2, overall page size in the KiB range)

- an L1 write-through data cache with 5 offset bits, 2-way set associative, 4 sets total, LRU replacement

Now, Consider the following code to set up a circular linked list (via an array of next pointers).

**#define NUM\_NODES <super-big-number>** // Power of 2, much bigger than 2<sup>20</sup>

| <pre>typedef struct node {     struct node *next; } node_t;</pre> | <pre>// A pointer to its own type, like a linked list // without the 'data' field, only a next ptr. // E.g., a cons with only a cdr. sizeof(node_t) = 4</pre> |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>node_t nodes[NUM_NODES];</pre>                               | // Now let's make an array of these pointers                                                                                                                  |

// Set up each 'next' pointer to point to another element in the array to make a circular // linked list. If we traversed the pointers, we'd visit every element and return to // the beginning. E.g., If NODES=4, this function could set the pointers so that we // would visit 0->1->2->3->0->etc OR 0->2->1->3->0->etc OR any other permutation. CreateCircularLinkedListOfPtrs(nodes);

SomeFunctionWhichTouchesTonsOfMemory(); // After this, nodes are <u>flushed</u> from cache & VM

node\_t \*ptr = &nodes[0]; for (int i = 0; i < NUM\_NODES; i++) ptr = ptr->next; // body (let's visit all the nodes once and then return home)

a) What single line of C would a **really** smart compiler interpret **the entire for loop** code as?

int i = NUM\_NODES;

lw \$s0, 0(\$s0)

- b) Assuming no optimization, what single MIPS instruction would the **body** of the for loop compile to if ptr is in \$s0?

- c) Given the cache/VM parameters above, fill in the following table for the **best** and **worst** case organizations of the linked list in memory based on what CreateCircularLinkedListOfPtrs might do.

- d) Just to do the instruction fetch (IF) for the instruction you wrote in (b), how many pages would be read and how many written to a software-controlled RAID 3 disk array in the worst case? Assume no disk failures.

|                        | Best Case   | Worst Case |

|------------------------|-------------|------------|

| # of Data Cache Misses | NUM_NODES/8 | NUM_NODES  |

| # of Page Faults       | NUM_NODES/P | NUM_NODES  |

Page we want is paged out, but no space & all pages dirty. Write old, read new. RAID 3W=RRWW.

3 2 \_\_\_\_\_ read, \_\_\_\_\_ written. 3 2

### Name:

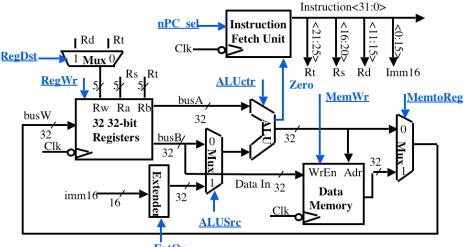

## F3) You have a case of the soiflz? Go to Datapathology! (18 pts, 24 mins)

On the right is the **single-cycle** MIPS datapath you all know and love. *Ignore pipelining for the question.* Your job is to modify the diagram to support a \_\_\_\_\_\_ Instruction<31:0>

new MIPS instruction to perform the following C code in **one** MAL instruction (ptr is an array of ints):

```

if(ptr[IMMEDIATE] == 0) {

ptr[IMMEDIATE] = 1;

}

```

We'll call our new instruction soiflz, for <u>store one if load zero</u>. If the word (that is stored IMMEDIATE integers past the base pointer in rs) is 0, then set that word to be 1.

a) Make up the syntax for the MAL MIPS instruction that does it (show an example where ptr lives in \$t0, and IMMEDIATE is 8). On the right, show the register transfer language (RTL) description of soiflz.

| Syntax         | RTL                                                                                      |

|----------------|------------------------------------------------------------------------------------------|

| soiflz 8(\$t0) | <pre>if(MEM[R[rs] + SignExtImm] == 0)     MEM[R[rs] + SignExtImm] = 1; PC = PC + 4</pre> |

b) Change as *little as possible* in the datapath above (draw your changes right in the figure) to enable soiflz and list all changes below. Your modification may use adders, shifters, muxes, wires, and new control signals. If necessary, you may replace existing labels. You may not need all boxes.

| (i)   | Add a mux whose output feeds WrEn and whose input is either MemWr or a comparison unit (nor) which compares Data Memory Data Out to zero, and is driven by a control line called soiflz.<br>WrEn=mux(A=MemWr, B={32 0s nor32(DataMemoryOut)}, Control=soiflz) |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (ii)  | Add a mux whose output is tied to Data Memory Data In, and whose input is either Data In or <b>0x00000001</b> , and is driven by <b>soiflz</b> . DataMemoryDataIn=mux(A=DataIn, B=0x00000001, Control=soiflz)                                                 |

| (iii) |                                                                                                                                                                                                                                                               |

| (iv)  |                                                                                                                                                                                                                                                               |

c) We now want to set all the control lines appropriately. List what each signal should be: an intuitive name or {0, 1, x - don't care}. Include any new control signals you added.

| RegDst | Reg₩r | nPC_sel | ExtOp | ALUSrc | ALUctr | MemWr | MemtoReg | soiflz |  |

|--------|-------|---------|-------|--------|--------|-------|----------|--------|--|

| x      | 0     | +4      | Sign  | Imm(1) | Add    | x     | x        | 1      |  |

d) Your smart friend argues that because of **this very instruction**, you should have a <u>fourth</u> instruction format (in addition to R, I and J). There's a clear downside: it would cause more complexity with control & datapath. That said, what would be the upside?

Since you only need 1 register, you could widen the immediate and handle larger offsets.

## F4) Please Pass Professor's Pretty Pipeline-pourri Problem... (30 pts, 42 min)

Given a standard five (5) stage pipelined processor with:

- No Forwarding

- Stalls on ALL data and control hazards; no out-of-order execution ; non-delayed branches

- Branch comparison occurs during the second stage; instructions are not fetched until branch comparison is done

- Memory CAN be read & written on the same clock cycle

- The same register CAN be read and written on the same clock cycle

- a) *Fill in the corresponding pipeline stages* (F,D,E,M,W) at the appropriate times in the table below for the following six MIPS instructions assuming the above properties of your CPU. You don't need to fill anything in for instruction (7).

|                              | Cycle |   |   |   |   |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

|------------------------------|-------|---|---|---|---|----------|---|----------|----------|----|----|-----|----|----|----|----|----|----|----|

| Instruction                  | 1     | 2 | 3 | 4 | 5 | 6        | 7 | 8        | 9        | 10 | 11 | 12  | 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| (1) add \$s0 \$s1 \$t0       | F     | D | Е | М | W |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

|                              |       | t |   |   | S |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

|                              |       | 0 |   |   | 0 |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

|                              |       | s |   |   |   |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

|                              |       | 1 |   |   |   |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

| (2) addi \$t0 \$t0 4         |       | F | D | Е | М | W        |   |          |          |    |    |     |    |    |    |    |    |    |    |

|                              |       |   | t |   |   | t        |   |          |          |    |    |     |    |    |    |    |    |    |    |

|                              |       |   | 0 |   |   | 0        |   |          |          |    |    |     |    |    |    |    |    |    |    |

| (3) sw \$s0 0(\$t1)          |       |   | F | F | D | Е        | М | W        |          |    |    |     |    |    |    |    |    |    |    |

| (0) 2 +20 0(+01)             |       |   |   |   | s |          |   | М        |          |    |    |     |    |    |    |    |    |    |    |

|                              |       |   |   |   | 0 |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

|                              |       |   |   |   | t |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

|                              |       |   |   |   | 1 |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

| (4) and \$t1 \$t1 \$t2       |       |   |   |   | F | D        | Е | М        | W        |    |    |     |    |    |    |    |    |    |    |

|                              |       |   |   |   |   | t        |   |          | t        |    |    |     |    |    |    |    |    |    |    |

|                              |       |   |   |   |   | 1        |   |          | 1        |    |    |     |    |    |    |    |    |    |    |

|                              |       |   |   |   |   | t        |   |          |          |    |    |     |    |    |    |    |    |    |    |

|                              |       |   |   |   |   | 2        |   |          |          |    |    |     |    |    |    |    |    |    |    |

| (5) lw \$t2 4(\$t1)          |       |   |   |   |   | F        | F | F        | D        | Е  | М  | Wt  |    |    |    |    |    |    |    |

| (0) = +0= =(+0=)             |       |   |   |   |   |          |   |          | t        |    |    | 2   |    |    |    |    |    |    |    |

|                              |       |   |   |   |   |          |   |          | 1        |    |    |     |    |    |    |    |    |    |    |

| (6) bne \$t2 \$t1 -6 #goto 1 |       |   |   |   |   |          |   |          | F        | F  | F  | Dt1 | Е  | М  | W  |    |    |    |    |

|                              |       |   |   |   |   |          |   |          |          |    |    | t2  |    |    |    |    |    |    |    |

| (7) sub \$s0 \$s0 \$t2       |       | 1 | I | 1 | 1 | <u> </u> |   | <u> </u> | <u> </u> | 1  | 1  | 1   | 1  |    |    |    |    |    |    |

|                              |       |   |   |   |   |          |   |          |          |    |    |     |    |    |    |    |    |    |    |

Cycle

- b) Assuming we've been in this loop for 1000 iterations, how many cycles does it take to evaluate fact igop? lock(&lockA); lock(&lockB); c) You (as the one who wrote the code in part (a)) are pretty unhappy with all the hazards you discoveled k (&lockA); when filling out the table. Suddenly, Sir Mips-a-lot – a representative strate drage and shouts: "Don't sulk!! We just implemented delayed branches!". Youlgedide to fit binstruction (2) instruction (2) instructi many cycles to evaluate each loop? (because (3) still has to wait on (1) for \$50 to be written, the nop that used to follow the branch swaps with (2), AND there's now a hazard from \$t0 being written by the addi (the old 2) to 1 that causes a newly-introduced delay of 2 cycles to clear the hazard) perpendicular magnetic recording (PMR) d) What recent breakthrough allows improved bit density on disk drives? (1 / ((1-4/5) + (4/5//16)) = 4xe) What's the speedup (over a 1-core machine) for a 20%-serial program on a 16-core machine? Deadlock if both grab their 1<sup>st</sup> lock but not 2<sup>nd</sup>.

- f) Two threads run cal and bears below. What can go wrong and how do we fix it?

- Fix by reordering lock acquires or w/CVs & logic.

| Na | me:Answer Key Login: cs61c                                                                                                                                                                                                                                  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| g) | A processor run on a particular benchmark<br>has the instruction mix and CPI shown in the table<br>at the bottom right. <i>How many times faster</i> would<br>the benchmark run if we quadruple $\frac{1}{2} \mathbf{x}$<br>the CPI of the ALU from 2 to 8? |

| h) | Which is <i>the best way</i> to communicate with a remote <b>interrupts</b><br>sensor measuring lunar eclipses, via polling or interrupts?                                                                                                                  |

| i) | What protocol guarantees delivery on a network?                                                                                                                                                                                                             |

| j) | Simpler, it does the load-balancing for us What is one reason MapReduce <i>is better than</i> MPI?                                                                                                                                                          |

|        | Frequency | CPI               |

|--------|-----------|-------------------|

| Memory | 30%       | 4                 |

| Branch | 20%       | 4                 |

| ALU    | 50%       | $2 \rightarrow 8$ |