1

Fall 1996

D.E. Culler

# CS 152 Midterm I

Your Name:\_\_\_\_\_

ID Number:\_\_\_\_\_

Discussion Section:\_\_\_\_\_

You may bring one double-sided pages of notes and you may use a calculator, but no book or computer. Please print your name clearly on the cover sheet and on every page. Show your work. Write neatly and be well organized. It never hurts to make it easy to grade.

Good luck.

| Problem | Possible | Score |

|---------|----------|-------|

| 1       | 25       |       |

| 2       | 20       |       |

| 3       | 25       |       |

| 4       | 20       |       |

| 5       | 10       |       |

| Total   | 100      |       |

Mean: 69, Max 97

Distribution: 100 - 85 (11), 84 - 70 (21), 69 - 55 (24), 54 - 40 (7), 39 - (2)

## Problem 1 (25 points)

1a [5] State the five major components of a computer (according to Patterson and Hennessey).

- 1. Processor datapath

- 2. Processor Control

- 3. Memory

- 4. Input

- 5. Output

1b [5]: Assemble the following MIPS instruction into its binary machine representation

- XORI \$15, \$0, 0x8000

- answer: op(6) rsrtimmediate

## 001110 00000 01111 1000 0000 0000 0000

1c [5]: Decode your answer to 1b as a 32-bit 2's-complement integer

a)  $2^{29} + 2^{28} + 2^{27} + 2^{20}$  b)  $2^{30} - 2^{27} + 31 \times 2^{15}$  c)  $7 \times 2^{27} + 31 \times 2^{20}$  d)  $14 \times 2^{27} + 31 \times 2^{15}$

1d [5]: Decode your answer to 1b as an single precision IEEE floating-point number

a)  $2^{-71} \times \frac{31}{256}$  b)  $2^{-15} \times \frac{31}{256}$  c)  $2^{-15} \times \frac{287}{256}$  d)  $2^{112} \times \frac{287}{256}$

####

Grading: 1a) 1 point for each component; 1b) 1 point for each field; 1c), 1d) hit or miss for multiple choice.

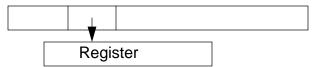

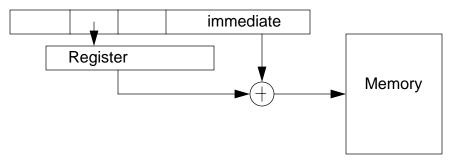

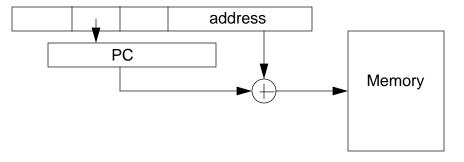

1e[5] What are the four basic <u>addressing modes</u> supported by the MIPS R3000 instruction set? Draw a diagram of each. (Do not include the special cases that arise from setting one of the operands to zero.)

register-addressing: value is contained in a register specified in the instruction

base (or displacement) addressing

immediate addressing: value is contained in the instruction

|  |  | immediate |

|--|--|-----------|

|  |  |           |

PC-relative addressing: PC <- PC + sign\_ext(Imm16)

Points: 1 for each type. -2 for lack of diagrams, or lack of description. Other addressing modes were also given credit, if labeled correctly.

Problem 2 (20 points). You have been running an important program over and over on a 33 MHz DEC 5000 and you decide that you want to understand its performance. So you run it on a detailed simulator and collect the following instruction mix and breakdown of costs for each instruction type.

| Instruction Class    | Frequence (%) | Cycles |  |

|----------------------|---------------|--------|--|

| Arithmetic / logical | 50            | 1      |  |

| Load                 | 20            | 2      |  |

| Store                | 10            | 2      |  |

| Jump                 | 10            | 1      |  |

| Branch               | 10            | 3      |  |

2.a. Calculate the CPI and MIPS for this program.

answer: CPI = 1.5 = 0.5 x 1 + 0.2 x 2 + 0.1 x 2 + 0.1 + 1 + 0.1 x 3, 22 MIPS

Points: +6 for correct answer

2.b. Suppose you turn on the optimizer and it eliminates 20% of the arithmetic/logic instructions (i.e. 10% of the instructions overall), but does not affect the other instruction classes. What is the speedup on this program with the optimizer. (Be sure you state and use the correct definition of speedup and show your work.)

a) 0.93 b) 1.07 c) 1.40 d) 1.55 e) none of these

Answer:

cycles per equivalent of average old instruction = 1.4

= 0.4 x 1 + 0.2 x 2 + 0.1 x 2 + 0.1 + 1 + 0.1 x 3.

speedup = 1.5 / 1.4 = 1.05

Points: + 6 for correct answer

2c. Calculate the CPI and MIPS for the optimized version of this program. Show your work. Compare your result to that of 2a and explain the change.

Answer CPI = 1.55, 21.2 MIPS. The program spends more of its time executing slow instruction, although there are fewer instructions overall.

Points: +8 for correct answer

Problem 3. (25 points) Complete the skeleton of MIPS assembly language below, generated by GCC for the following C function. All jumps and branches are delayed. Simple pseudo-ops are used to make it more readable. Annotate the instructions to explain what they do in the C program.

| int scale (int *A, int n, int x)<br>{ |                  | nt n, int x)               | <u>Register Usage</u><br>\$4 - *A                                       |

|---------------------------------------|------------------|----------------------------|-------------------------------------------------------------------------|

|                                       | nt i;            |                            | \$5 - n                                                                 |

| f                                     | or (i=0; i<ı     | , ,                        | \$6 - x                                                                 |

| }                                     |                  | = A[i]*x;                  |                                                                         |

| }                                     |                  |                            |                                                                         |

|                                       |                  |                            |                                                                         |

|                                       |                  |                            |                                                                         |

| .ent                                  | scale            |                            |                                                                         |

| scale                                 |                  |                            |                                                                         |

|                                       | subu             | \$sp,\$sp,8                | Adjust Stack pointer                                                    |

|                                       | blez             | \$5, <u>\$L3</u>           | test $n = 0$ , if so fall through                                       |

| \$L5:                                 | move             | \$7, <u>\$0</u>            | <u>i = 0</u>                                                            |

| φ∟J.                                  | sll              | \$3,\$7, <u>2</u>          | multiple i by 2                                                         |

|                                       | addu             | \$3,\$3,\$4                | address of A[i]                                                         |

|                                       | lw               | \$2, <u>0(\$3)</u>         | fetchA[i]                                                               |

|                                       | #nop             |                            |                                                                         |

|                                       | mult             | \$6,\$2                    | <u>A[i]*x</u>                                                           |

|                                       | -                | <u>\$8</u>                 | extract low 32 bits                                                     |

|                                       | #nop             | <u> </u>                   |                                                                         |

|                                       | addu             | \$7,\$7,1                  | increment i                                                             |

|                                       | slt              | \$2,\$7, <u>\$5</u>        | test i <n< td=""></n<>                                                  |

|                                       | bne<br><u>sw</u> | \$2,\$0,\$L5<br>\$8,0(\$3) | if i <n go="" loop<br="" of="" to="" top="">store A[i] &lt;- A[i]*x</n> |

| \$L3:                                 | 311              | ψ0,0(ψ3)                   |                                                                         |

| Ψ20.                                  | addu             | <u>\$sp,\$sp,8</u>         | restore stack                                                           |

|                                       | j                | <u>\$31</u>                | return                                                                  |

|                                       | ,<br>#nop        |                            | -                                                                       |

|                                       | end sc           | ale                        |                                                                         |

Points: 3 points for Register Usage; 18 points for instruction fill-ins; 4 points for explanation on left side

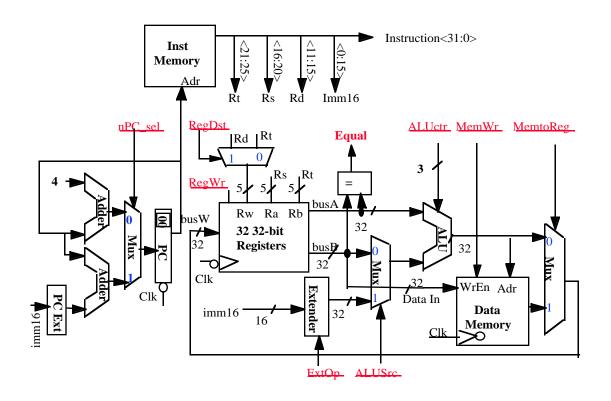

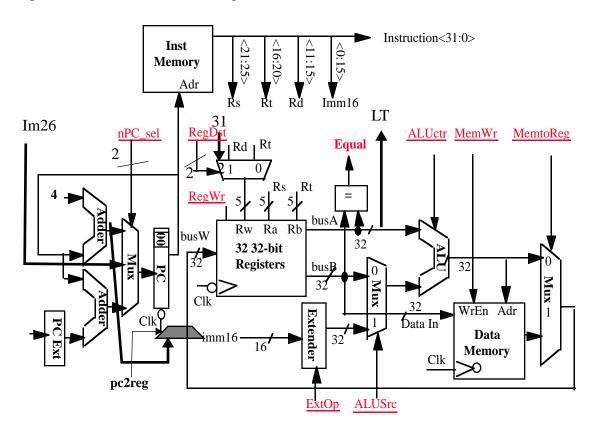

The Single-Cycle processor developed in class below (which was very similar to the one in the book) supports the instructions in the table below. (Note that, as in the virtual machine, the branch is not delayed.)

| op   rs   rt   rd   shamt   funct = MEM[ PC ]<br>op   rs   rt   $Imm16 =$ |                                                                             |                 |  |  |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------|--|--|--|

| inst                                                                      | Register Transfers                                                          |                 |  |  |  |

| ADDU                                                                      | R[rd] <- R[rs] + R[rt];                                                     | $PC \le PC + 4$ |  |  |  |

| SUBU                                                                      | R[rd] <- R[rs] - R[rt];                                                     | $PC \le PC + 4$ |  |  |  |

| ORi                                                                       | $R[rt] \le R[rs] + zero\_ext(Imm16);$                                       | $PC \le PC + 4$ |  |  |  |

| LW                                                                        | R[rt] <- MEM[ R[rs] + sign_ext(Imm16)];                                     | $PC \le PC + 4$ |  |  |  |

| SW                                                                        | MEM[ R[rs] + sign_ext(Imm16)] <- R[rs];                                     | $PC \le PC + 4$ |  |  |  |

| BEQ                                                                       | 3EQ if $(R[rs] == R[rt])$ then PC $\leq -PC + sign_ext(Imm16) \parallel 00$ |                 |  |  |  |

|                                                                           | else PC <- PC + 4                                                           |                 |  |  |  |

Consider adding the following instructions to our subset: ADDIU, AND, BLTZ, JAL. On the following pages, (1) write the register transfers for the new instructions, (2) modify the datapath to support these instructions and (3) specify the control points for each of the new instructions.

| op   rs   rt   rd   shamt   funct = MEM[ PC ]<br>op   rs   rt   Imm16 = |                                                    |                                                 |  |  |  |  |

|-------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------|--|--|--|--|

| inst                                                                    | Register Transfers                                 |                                                 |  |  |  |  |

| ADDIU                                                                   | R[rt] <- R[rs] + SignExt(Imm16)                    | $PC \le PC + 4$                                 |  |  |  |  |

| AND                                                                     | $R[rd] \leq R[rs]$ and $R[rt]$ ;                   | $PC \le PC + 4$                                 |  |  |  |  |

| BLTZ                                                                    | if $R[rs]_{31} = 1$ then PC <- PC + SignExt(Imm16) | 00 else PC <- PC + 4                            |  |  |  |  |

| JAL                                                                     | $R[31] \le -PC + 4$                                | $PC \le PC_{3128} \parallel Imm26 \parallel 00$ |  |  |  |  |

No changes to the datapath are required the three arithmetic/logical instructions, except the ALU needs to support AND. There is already the capability to sign extend immediates and to operate on pairs of registers.

To support the BLTZ we need to:

• detect R[rs] < 0, this is just the sign bit of bus\_A

To support JAL, we need to:

- provide a path from the PC+4 adder onto the register input bus (bus\_w)

- provide 31 as the destination register number.

Problem 4 (cont)

| TABLE 1 | • |

|---------|---|

|---------|---|

|       | Ext  | ALUsrc | ALUCtr | MemWr | Mem2Reg | PC2Reg | RegDst | RegWr | nPC |

|-------|------|--------|--------|-------|---------|--------|--------|-------|-----|

| ADDIU | sign | 1      | add    | 0     | 0       | 0      | 0      | 1     | 0   |

| AND   | х    | 0      | AND    | 0     | 0       | 0      | 1      | 1     | 0   |

| BLTZ  | Х    | х      | Х      | 0     | Х       | Х      | Х      | 0     | lt  |

| JAL   | х    | Х      | Х      | 0     | Х       | 1      | 2      | 1     | 2   |

Points: 8 points for register transfers; 8 points for alterations to datapath; 4 points for control signals

## Problem 5 (10 points)

Write a series of instructions to MIPS instructions to perform a signed 64-bit SLT. The operands are passed in registers A1:A0 and A3:A2 with the MSW in the higher numbered register. The result should be returned in register t0 with the same convention. Explain why your code works.

/\* t0 = a1:a0 <? a3:a2 \*/

BNE a1, a3, L:slt t0, a1, a3sltu v0, a0, a2

```

L:

```

Points: +5 for sltu for least significant word; +5 for understanding when to use sltu comparator on least significant word (when a1 = a3). No points were taken off if you did not use the delay slots efficiently.