## UNIVERSITY OF CALIFORNIA AT BERKELEY

BERKELEY • DAVIS • IR VINE • LOS ANGELES • RIVERSIDE • SAN DIEGO • SAN FRANCISCO

Department of Electrical Engineering and Computer Sciences

SANTA BARBARA • SANTA CRUZ

CS 150 - Spring 1994 Prof. A. R. Newton

## Quiz 2 Room 145 Dwinelle, Tuesday 4/5 (Open Katz, Calculators OK, 1hr 20min)

Include all final answers in locations indicated on these pages. Use reverse side of sheets for all working. If necessary, attach additional sheets by staple at the end. BE SURE TO WRITE YOUR NAME ON EVERY SHEET.

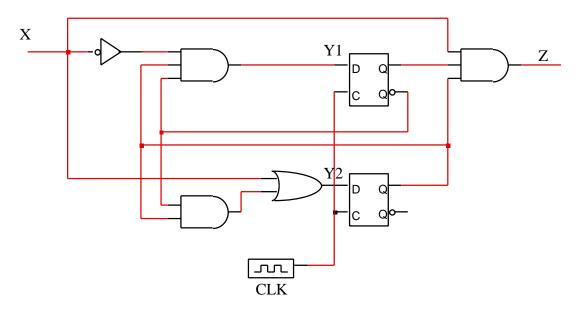

(1) Consider the logic schematic diagram shown below:

- (a) Is this a Moore or Mealy machine?  $Mealy_(2pts)$

- (b) What are the **next-state** and **output equations** for this machine? (9pts)

(i)

$$Y1 = \___y1' \cdot y_2 \cdot X'$$

\_\_\_\_\_

(ii)  $Y2 = \__X + y1' \cdot y2$ \_\_\_\_\_

(iii)  $Z = \__y1 \cdot y2 \cdot X$ \_\_\_\_\_

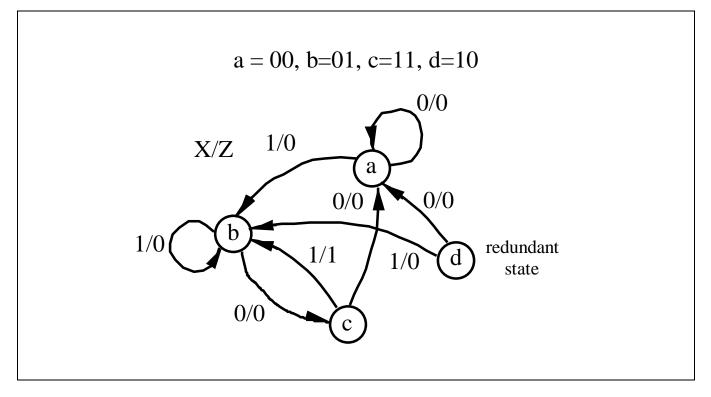

(c) Draw a state transition graph (STG) for the machine showing all possible states and all possible transitions (7pts)

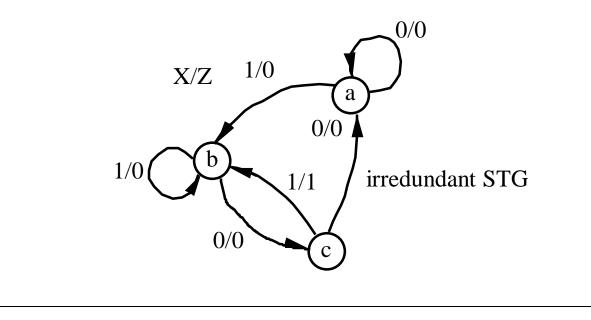

(d) **Does the machine contain any redundant states?** If so, which state(s) are redundant and how can they be removed? **Draw an irredundant STG for the machine.** (7pts)

Yes, State d is redundant because it is identical to State a (has the same next state and outputs). By removing State d there is no change to the behavior of the machine.

#### Your Name: \_

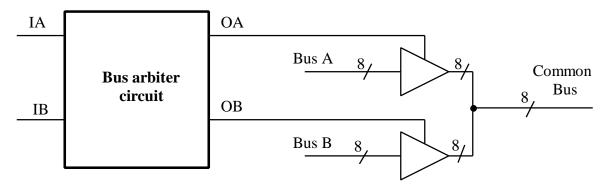

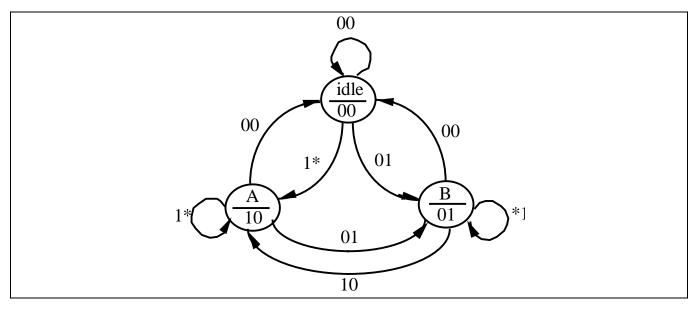

(2) You are to design a bus arbiter that operates as follows. When inputs IA IB = 0.0 the circuit either goes into the idle state (outputs OA OB = 0.0, disabling both Bus A and Bus B buffers), or remains in the idle state. When inputs IA IB change to 1 0 or 1 1 the circuit goes into State A (outputs OA OB = 1.0 enabling the Bus A buffers and disabling the Bus B buffers.) When inputs IA IB change to 0 1 while in the idle state, the circuit goes to State B (outputs OA OB = 0.1 disabling Bus A buffers and enabling Bus B buffers.) To go from State A to State B requires input IA IB = 01, and to go from State B to State A requires inputs IA IB = 10.

(a) Construct a State Transition Graph for the bus arbiter in Moore form. (5pts)

(b) Derive a **State Transition Table** from your graph, also in Moore form. (3pts)

|      | IA IB |    |    |    |      |  |  |

|------|-------|----|----|----|------|--|--|

| PS   | 00    | 01 | 11 | 10 | OAOB |  |  |

| Idle | Idle  | В  | Α  | A  | 00   |  |  |

| А    | Idle  | В  | А  | A  | 10   |  |  |

| В    | Idle  | В  | В  | Α  | 01   |  |  |

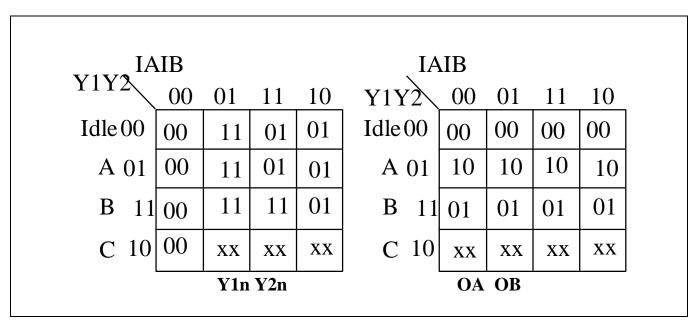

(c) If the idle state is encoded as Y1 Y2 = 0 0, State A is encoded as Y1 Y2 = 0 1 and State B as Y1 Y2 = 1 1, derive the **Karnaugh maps for the next-state and output functions.** (4pts)

(d) If the machine is to be implemented using JK flip-flops, obtain the Karnaugh maps for the JK flip-flop excitation inputs. Write the excitation input and external output equations for the design. (10pts)

| (10pts)                   |    |    |    |    |         |    |    |    |    |  |

|---------------------------|----|----|----|----|---------|----|----|----|----|--|

| \IA                       |    |    |    |    | \IA     | IB |    |    |    |  |

| Y1Y2                      | 00 | 01 | 11 | 10 | Y1Y2    | 00 | 01 | 11 | 10 |  |

| Idle 00                   | 00 | 11 | 01 | 01 | Idle 00 | XX | XX | XX | XX |  |

| A 01                      | 0x | 1x | 0x | 0x | A 01    | x1 | x0 | x0 | x0 |  |

| B 11                      | XX | XX | XX | XX | B 11    | 11 | 00 | 00 | 10 |  |

| C 10                      | x0 | XX | XX | XX | C 10    | 1x | XX | XX | XX |  |

|                           |    | J1 | J2 | 1  | J       | K1 | K2 |    |    |  |

| $J1 = \_IA' \bullet IB\_$ |    |    |    |    |         |    |    |    |    |  |

| $J2 = \_IA + IB \_$       |    |    |    |    |         |    |    |    |    |  |

| K1 =IB'                   |    |    |    |    |         |    |    |    |    |  |

| K2 =IA' • IB'             |    |    |    |    |         |    |    |    |    |  |

| OA=_Y1' • Y2              |    |    |    |    |         |    |    |    |    |  |

| OB =Y1                    |    |    |    |    |         |    |    |    |    |  |

|                           |    |    |    |    |         |    |    |    |    |  |

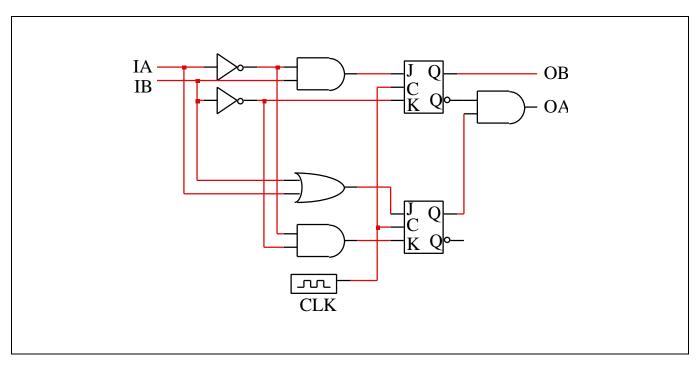

(e) Show a schematic diagram for the bus arbiter using positive edge-triggered JK flop flops. (3pts)

Extra space for Problem 2

| Yir | ı Yi | Ji | Ki |

|-----|------|----|----|

| 0   | 0    | 0  | X  |

| 0   | 1    | 1  | х  |

| 1   | 0    | x  | 1  |

| 1   | 1    | x  | 0  |

Page 5 of 10

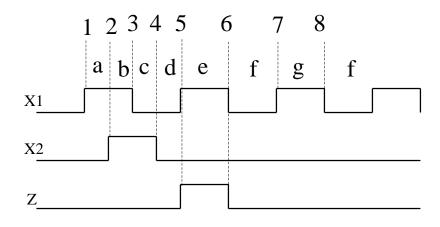

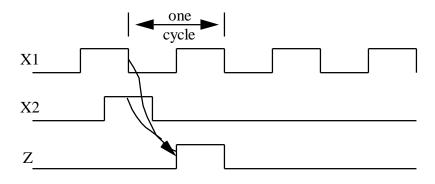

(3) Design a fundamental mode asynchronous circuit with two inputs and one output. Input X1 is driven by the system clock. Input X2 is an asynchronous input. If X2 is logic 1 when X1 changes from 1 to 0, then output Z follows the waveform of input X1 for one cycle (i.e. until X1 changes again from 1 to 0.) If X2 is a logic 0 when X1 changes from 1 to 0, then Z is a logic 0 until X1 changes again from 1 to 0. Example behavior is shown in the timing diagram below. The circuit should be designed so that it is logic hazard-free, has a race-free state assignment, and can recover from illegal or unused states.

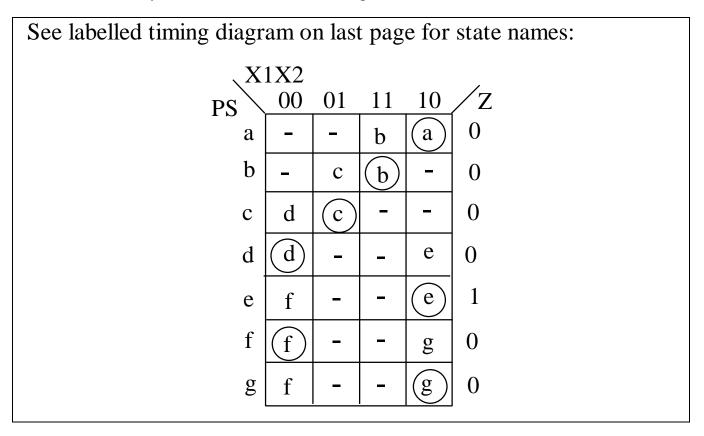

(a) Use the word description and timing diagram above to obtain a **primitive flow table** for the problem (hint: I used 7 symbolic states in Moore form) (4pts)

### Your Name: \_

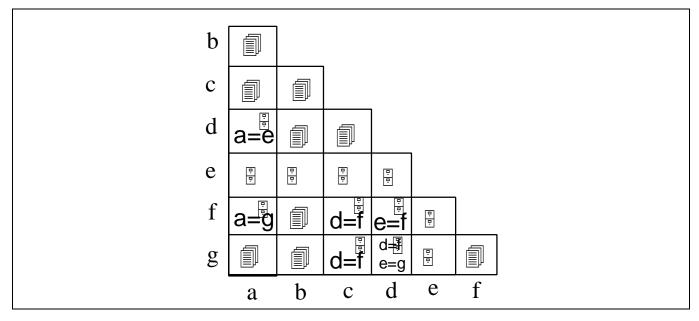

(b) Use an **implication table** to find all possible pairs of equivalent or compatible states (3pts).

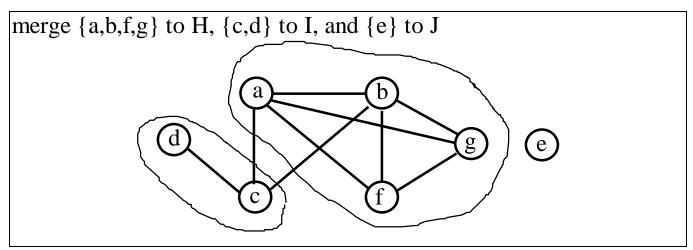

(c) Construct a merger diagram from the results of (b) and list the sets of mergeable states that will lead to the minimum number of states for the design. (3pts)

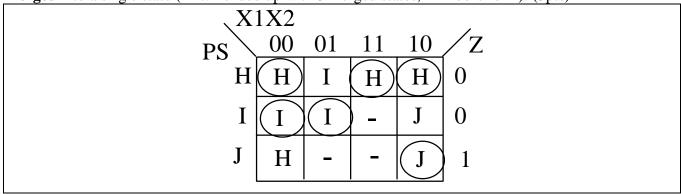

(d) Obtain a **reduced flow table** from the above, giving a **unique state name to each group of states merged** into a single state (hint: I ended up with 3 merged states, in Moore form). (3pts)

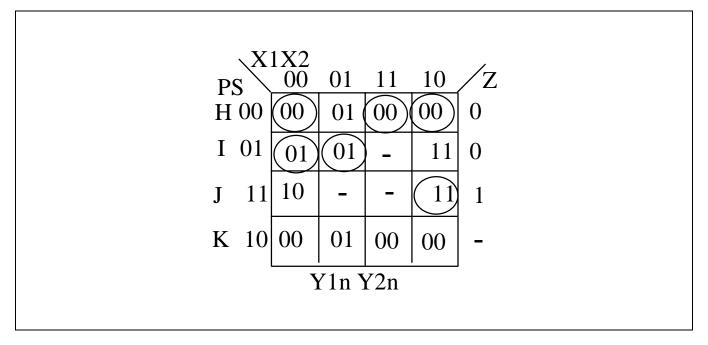

(e) Examine the reduced flow table and **add additional states if necessary to obtain a critical-racefree state assignment** for the circuit. (hint: requires two state bits) (3pts)

# $H = \{00\}, I = \{01\}, J = \{11\}, must add K = \{10\} for J-H$ transition.

(f) Construct a composite **Karnaugh map for the next-state and external output logic functions** from your state assignment. (3pts)

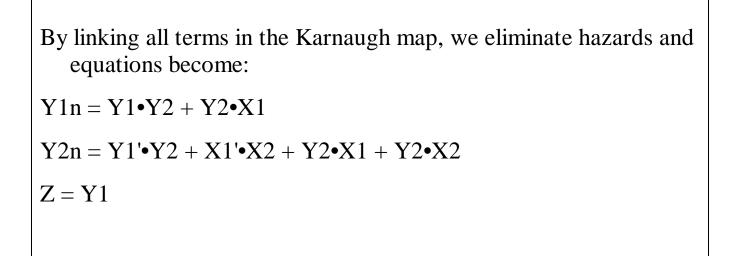

(g) Modify your combinational logic, if necessary, to **eliminate hazards** from the design. State what you are doing and why you are doing it. (2pts)

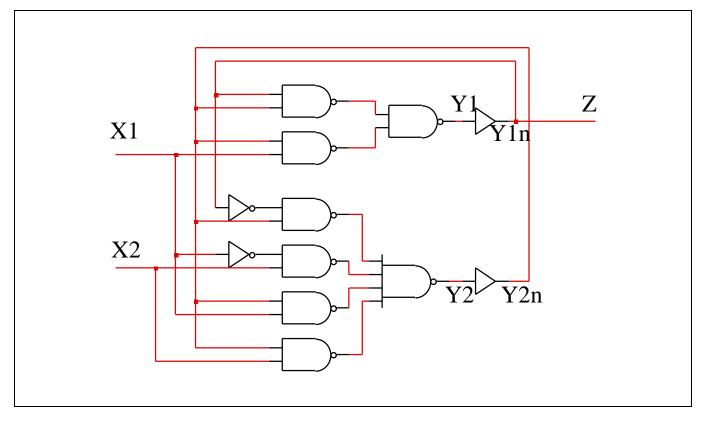

(h) Draw a **gate-level asynchronous sequential circuit diagram** for the design. Represent the asynchronous delay element(s) in feedback loops with a buffer symbol. (4pts)

Additional space for Problem 3