| Name | Solutions |

|------|-----------|

|------|-----------|

## EE40

## Midterm 3

# April 24, 2003

# PLEASE WRITE YOUR NAME ON EACH ATTACHED PAGE PLEASE SHOW YOUR WORK TO RECEIVE PARTIAL CREDIT PLEASE DO NOT LEAVE UNTIL EXAM PERIOD IS OVER

| Problem 1: 15 Points Possible |  |

|-------------------------------|--|

| Problem 2: 20 Points Possible |  |

| Problem 3: 15 Points Possible |  |

| Problem 4: 20 Points Possible |  |

| Problem 5: 20 Points Possible |  |

| Problem 6: 10 Points Possible |  |

| TOTAL: 100 Points Possible    |  |

#### **Problem 1**: 15 Points Possible

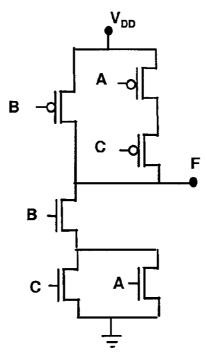

Determine whether the circuit below performs a logical operation. If it does, give the Boolean function it computes. If not, give a set of inputs that results in an invalid output.

For your convenience, 8 copies of this circuit are given on the next page. Assume that all PMOS transistors have source terminal on top, and all NMOS transistors have source terminal on the bottom.

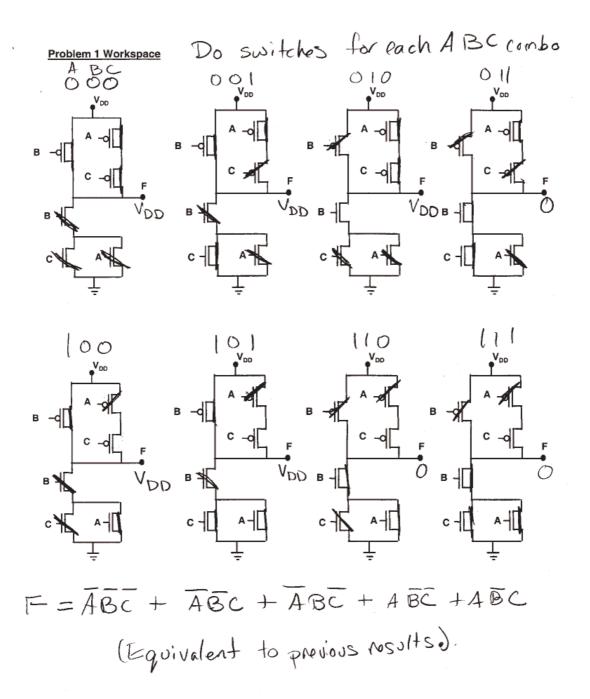

From looking at PMOS half: F=Vooif

B conducts OR (A conducts AND C conducts)

F=B+AC

From looking at Nmos half: F=O if

B conducts AND (A concludes OR C conducts)

F=B(A+C)

These agree by De Morgan's law; it is a logic circuit.

## **Problem 1 Workspace**

## Problem 2: 20 Points Possible

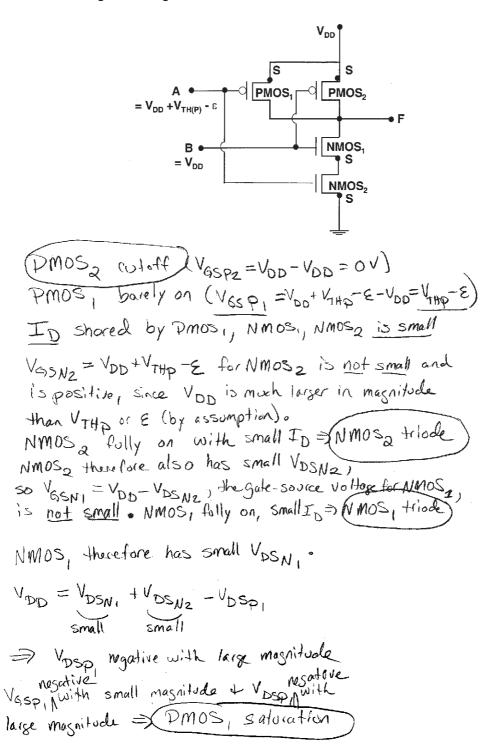

For the CMOS logic circuit below, determine the most probable mode of operation for each transistor. Assume that  $\epsilon$  is a very small positive number, and  $V_{DD}$  is much larger in magnitude than either  $V_{TH}$ .

| Name | Solutions |

|------|-----------|

|------|-----------|

#### **Problem 3:** 15 Points Possible

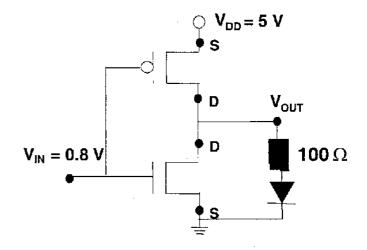

Consider the inverter at right, which turns on an LED when the output voltage is high.

I have put a resistor in series with the LED to limit the current so the LED doesn't burn.

But, the LED needs a current of at least 20 mA to light up.

I want the LED to light up for an input voltage as high as 0.8 V.

Will the LED light up for an input of 0.8 V?

W/L  $\mu$  C<sub>OX</sub> = 100 mA/V<sup>2</sup> for both transistors, V<sub>TH(N)</sub> = -V<sub>TH(P)</sub> = 1 V,  $\lambda$  = 0 V<sup>-1</sup> for both transistors, V<sub>F</sub> = 2 V for the LED (use large-signal model).

| Name | Solutions |  |

|------|-----------|--|

|      |           |  |

## Problem 4: 20 Points Possible

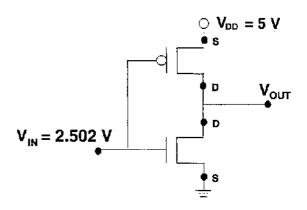

Consider the CMOS inverter at right, with

W/L  $\mu$  C<sub>OX</sub> = 1 mA/V<sup>2</sup> for both transistors, V<sub>TH(N)</sub> = -V<sub>TH(P)</sub> = 1 V,  $\lambda$  = **0.01 V**<sup>-1</sup> for both transistors.

For this inverter,  $V_M = 2.5 \text{ V}$ .

- a) Find  $V_{OUT}$  for  $V_{IN}$  = 2.502 V. Hint for guessing modes: Notice that  $V_{IN}$  is close to  $V_{M}$ .

- b) Find the slope of the  $V_{OUT}$  vs.  $V_{IN}$  curve in this region, given by

$$\frac{\Delta V_{\text{OUT}}}{\Delta V_{\text{IN}}} = \frac{V_{\text{OUT}}(\text{for Vin} = 2.502 \text{V}) \cdot V_{\text{M}}}{2.502 \text{V} \cdot V_{\text{M}}}$$

Since we have unloaded inverter with

Vin close to  $V_{\text{M}}$ , assume "region C" with

both transistors in saturation.

$$I_{\text{DN}} = \frac{1}{2} \cdot \frac{1}{MA} \frac{1}{V^2} (2.502 \text{V} - 1 \text{V})^2 (1 + 0.01 \text{V}_{\text{DSN}})$$

$$I_{\text{DP}} = \frac{1}{2} \cdot \frac{1}{MA} \frac{1}{V^2} (2.502 \text{V} - 1 \text{V})^2 (1 - 0.01 \text{V}_{\text{DSN}})$$

$$I_{\text{DP}} = \frac{1}{2} \cdot \frac{1}{MA} \frac{1}{V^2} (2.502 \text{V} - 5 \text{V} - 1 \text{V})^2 (1 - 0.01 \text{V}_{\text{DSN}})$$

$$I_{\text{DP}} = \frac{1}{2} \cdot \frac{1}{MA} \frac{1}{V^2} (2.502 \text{V} - 5 \text{V} - 1 \text{V})^2 (1 - 0.01 \text{V}_{\text{DSN}})$$

$$I_{\text{DP}} = \frac{1}{2} \cdot \frac{1}{MA} \frac{1}{V^2} (2.502 \text{V} - 2.5 \text{V})$$

$$I_{\text{DN}} = \frac{1}{2} \cdot \frac{1}{MA} \frac{1}{V_{\text{DN}}} = \frac{1}{2} \cdot \frac{1}{MA} \frac{1}{V_{\text{DN}}} = \frac{1}{2} \cdot \frac{1}{MA} \frac{1}{V_{\text{DN}}}$$

$$I_{\text{DN}} = \frac{1}{2} \cdot \frac{1}{MA} \frac{1}{V_{\text{DN}}} = \frac{1}{2} \cdot$$

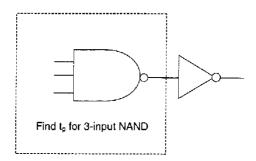

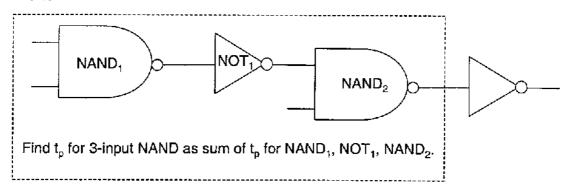

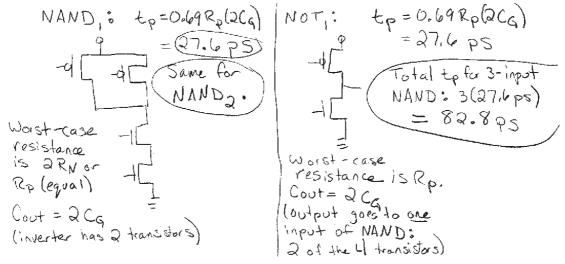

#### Problem 5: 20 Points Possible

Find the propagation delay for this 3-input NAND gate with inverter load,

where the 3-input NAND is implemented using two 2-input NAND gates and an inverter:

Compute the propagation delay  $t_p$  for the 3-input NAND as the sum of the worst-case propagation delays of the individual gates inside.

Use  $R_N$  = 1  $k\Omega,~R_P$  = 2  $k\Omega,$  and  $C_G$  = 10 fF per transistor. Ignore interconnect capacitance.

| Name | Solutions  |

|------|------------|

| Name | 3010110115 |

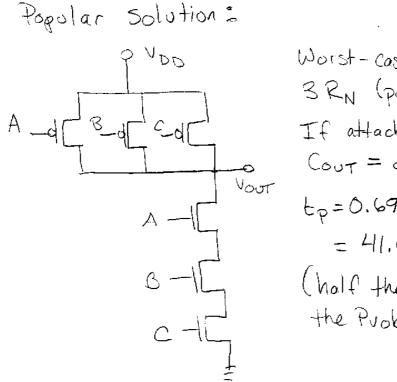

#### Problem 6: 10 Points Possible

Design a circuit, using only NMOS and PMOS transistors (and a power supply), that performs the 3-input NAND function with **shorter** worse-case propagation delay than the implementation given in Problem 5, when a single inverter is attached as the output load.

Assume that your transistors have the same characteristics as those I Problem 5.

Use  $R_N$  = 1  $k\Omega,~R_P$  = 2  $k\Omega,$  and  $C_G$  = 10 fF per transistor. Ignore interconnect capacitance.

Provide your design and its worst-case propagation delay with single inverter output load.

Worst-case resistances

3 RN (poll-down)

If attached to inverter,

Cout = 2 Cq

Ep=0.69(3RN)(2Cq)

= 41.4 ps

(half the delay of

the Problem 5 analysis)

| Name  | Solutions |  |

|-------|-----------|--|

| manne | SOIULIONS |  |

## **Fun Corner**

It's picture time again! If you finish early, please don't get up and disturb students in your row. Instead, show off your artistic/comedic ability here.