## UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences

E. Alon

Midterm Thursday, March 12, 2009 EECS 240 SPRING 2009

You should write your results on the exam sheets only. Partial credit will be given only if you show your work and reasoning clearly.

Name:

Solutions

SID:

- Problem 1 \_\_\_\_/ 13

- Problem 2 \_\_\_\_/ 10

- Problem 3 \_\_\_\_/ 9

- Total \_\_\_\_/ 32

## Problem 1 (13 points) Capacitance and SNR

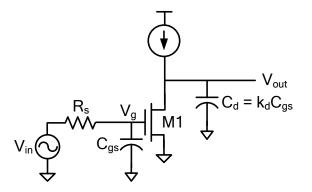

In this problem we will look at optimizing the SNR of the amplifier shown below.

You should use the following assumptions and simplifications to solve this problem:

- The input of the amplifier  $(V_{in})$  is a sinusoid with an angular frequency of  $\omega_{in}$  and an amplitude of  $A_{in}$ .

- The transistor is biased with a fixed V\* so that its gain  $(g_m r_o)$  is  $A_{v0}$ .

- Assume R<sub>s</sub> is noiseless, and ignore all capacitors except those shown in the figure.

- You should assume that  $1/(r_0C_d) \gg \omega_{in}$ . In other words,  $V_{out}(j\omega_{in})/V_g(j\omega_{in}) = A_{v0}$ .

- Your final answers should be a function of only k, T,  $\gamma$ ,  $\omega_{in}$ ,  $A_{in}$ ,  $k_d$ ,  $A_{v0}$ ,  $R_s$ , and  $C_{gs}$ .

- a) (4 pts) What is the voltage noise variance  $\overline{v_{on}^2}$  at the output of the amplifier?

b) (4 pts) What is the mean-squared signal voltage  $\overline{V_{out}^2}$  at the output of the amplifier?

$$V_{in} \underbrace{\bigoplus_{i=1}^{R_{2}} V_{3}}_{I} \underbrace{V_{3}(i)}_{V_{i,1}(s)} = \frac{1}{1 + s R_{3}(s)}$$

$$\left\| \frac{V_{3}(jw_{in})}{V_{in}(jw_{in})} \right\|_{i=1}^{2} \frac{1}{1 + W_{i,2}^{2} R_{3}^{2}(s)^{2}}$$

$$V_{out} = AvoV_{3} \qquad \overline{V_{in}^{2}} = \frac{A_{in}^{2}}{2}$$

$$\overline{V_{out}}^{2} = A_{vo}^{2} \cdot \frac{A_{in}^{2}}{2} \cdot \frac{1}{1 + W_{i,2}^{2} R_{3}^{2}(s)^{2}}$$

c) (5 pts) Keeping the V\* of the transistor fixed, what value of C<sub>gs</sub> maximizes the SNR  $\overline{V_{out}^2}/\overline{v_{on}^2}$  at the output of the amplifier?

$$\frac{V_{out}^2}{V_{out}^2} = \frac{A_{vv}^2 \cdot A_{vv}^2/2}{(1+w_{vv}^2 R_s^2(g_s^2))} \cdot \frac{C_{gs}}{kT} \cdot \frac{kd}{\lambda A_{vv}}$$

$$\frac{\partial SNR}{\partial l_{5}s} = \frac{(1 + w_{in}^{2} R_{s}^{2} l_{5s}^{2}) - 2(g_{5} w_{in}^{2} - R_{s}^{2} \cdot l_{5s}}{(1 + w_{in}^{2} R_{s}^{2} (g_{s}^{2})^{2}} = 0$$

$$|+w_{in}^{2}R_{s}^{2}(y_{s}^{2} = 2w_{in}^{2}R_{s}^{2}(y_{s}^{2})$$

$$W_{in}^{2}R_{s}^{2}(y_{s}^{2} = 1)$$

$$C_{gs} = \frac{1}{w_{in}R_{s}}$$

$$(i.e., w_{in} = \frac{1}{R_{s}(y_{s}, cpt)})$$

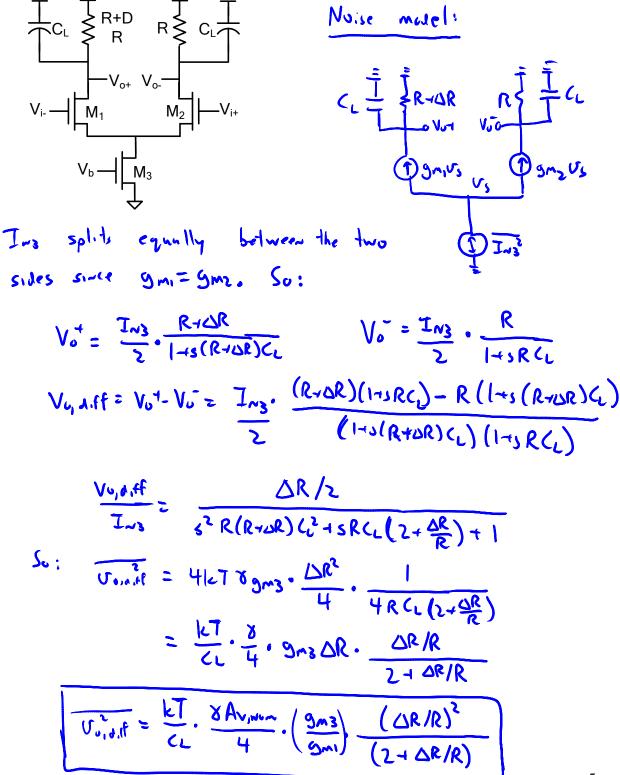

## Problem 2 (10 points) Noise

Considering only the noise current from M<sub>3</sub>, what is the variance of the differential voltage noise at the output of the amplifier shown below? You can ignore all the  $r_0$ 's of the transistors and all capacitors except those explicitly drawn in the schematic. You can assume that M<sub>1</sub> and M<sub>2</sub> are identical (i.e.,  $g_{m1} = g_{m2}$ ), and you should provide your answers in terms of k, T,  $\gamma$ , C<sub>L</sub>, ( $g_{m3}/g_{m1}$ ), ( $\Delta R/R$ ), and A<sub>v,nom</sub> = ( $g_{m1}R$ ).

5

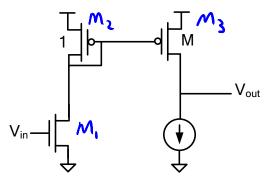

Problem 3 (9 points) Amplifier Design

a) (4 pts) Assuming that the V\* of the NMOS and PMOS transistors are  $V_n^*$  and  $V_p^*$  respectively and ignoring the  $r_0$  of all of the transistors, what is the nf of the amplifier shown above? In other words, relative to the noise current from the input transistor, what is the noise current density that flows into the amplifier's output? You should provide your answer in terms of  $V_n^*$ ,  $V_p^*$ , and M.

$$i_{N,i+1}^{2} = i_{N,m1} \cdot M^{2} + i_{N,m2} \cdot M^{2} + i_{N,m3}^{2}$$

$$nf = \frac{i_{N,m1}^{2}}{i_{N,m1} \cdot M^{2}} = 1 + \frac{i_{N,m2}}{i_{N,m1}} + \frac{i_{N,m3}^{2}}{i_{N,m1} \cdot M^{2}}$$

$$\frac{i_{N,m1}^{2}}{i_{N,m1}^{2}} = 4 k_{1} \times g_{m1} \Delta g_{1}$$

$$g_{m1} = 24 k_{1} \times g_{m2} \Delta g_{1}$$

$$g_{m2} = 210 / V_{N}^{*}$$

$$g_{m2} = 210 / V_{N}^{*}$$

$$i_{N,m3}^{*} = 4 k_{1} \times g_{m2} \Delta g_{1}$$

$$g_{m3} = M g_{m2}$$

$$f_{N,m3}^{*} = 4 k_{1} \times g_{m3} \Delta g_{1}$$

$$g_{m3} = M g_{m2}$$

$$f_{N,m3}^{*} = 4 k_{1} \times g_{m3} \Delta g_{1}$$

$$g_{m3} = M g_{m2}$$

$$f_{N,m3}^{*} = 4 k_{1} \times g_{m3} \Delta g_{1}$$

$$g_{m3} = M g_{m2}$$

$$f_{N,m3}^{*} = 1 + \frac{g_{m1}}{g_{m1}} + \frac{M g_{m2}}{M^{2} g_{m1}}$$

$$nf = 1 + (1 + \frac{1}{M}) - \frac{V_{N}^{*}}{V_{p}^{*}}$$

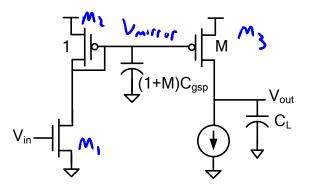

b) (5 pts) Now let's look at the stability of this amplifier under feedback using the model shown above (ignore the  $r_o$ 's and all capacitors except the ones shown in the model). If the amplifier is placed into unity-gain feedback with a closed-loop bandwidth of  $\omega_{gbw}$ , what is the maximum M that will provide at least 45° of phase margin? You should provide your answer in terms of  $\omega_{gbw}$  and the  $\omega_T$  of the PMOS transistors.

Pule at

$$V_{mirror}: W_{P2} = \frac{g_{M2}}{(1+M)C_{952}} = \frac{W_T}{(1+M)}$$

$W_{P2}$  is the num-dominant pule.

Dominant pule crocses over at  $W_{9bW} \left(=\frac{g_{M1}}{C_L}\right)$

$F_{cr} \geq 45^{U}$  phase marging wount:

$W_{P2} \geq W_{9bW}$

$\frac{W_T}{(-M)} \geq W_{9bW}$

$M \leq \frac{W_T}{W_{9bW}} = 1$