#### UNIVERSITY OF CALIFORNIA

## College of Engineering

### Department of Electrical Engineering and Computer Sciences

EE 143 Midterm Exam # 2

| Family Name                              | First Name                  |

|------------------------------------------|-----------------------------|

| Signature                                |                             |

| Make sure the exam paper has 10 pages    | including cover page        |

| This is a 90 minute exam (8 sheet of not | es allowed)                 |

| DO ALL WORK ON EXAM PAGES                |                             |

| Whenever possible, use sketches to illus | tarte your explanations,    |

| Numerical answers orders of magnitude    | off will receive no partial |

| Credit.                                  |                             |

| Problem 1 (30 points).                   |                             |

| Problem 2 (20 Points).                   |                             |

| Problem 3 (25 points).                   |                             |

| Problem 4 (25 points).                   |                             |

| TOTAL (100 points)                       |                             |

|                                          |                             |

| Problem 1 Lithography (30 points total)  |                             |

a. (10 points) Alignment Error calculation

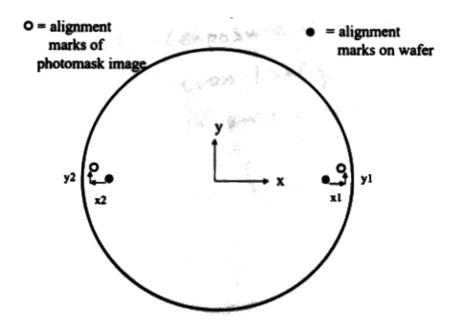

A wafer with 100 mm diameter has only two alignment marks lying exactly on the x-axis. The two diagonal alignment marks Al and A2 are near the edge of the wafer with overlay errors ( $x_1$ = + 1 urn,  $y_1$ = + 1 um) and ( $x_2$  = - 1 um,  $y_2$  = + 1 um).

Calculate numerical values (with algebraic sign and magnitude) of

- i. Run in/out misalignment

- ii. Rotation misalignment

- iii. Translation misalignment

- a. (10 points) An optical lithography process can produce a minimum printable feature (= k<sub>1</sub>

NA) and a useable Depth of Focus (= k2 NA)2 with k1 = 0.536 and k2=0.5.

A microfabrication process requires a printable minimum feature of 0.3 um with a usable Depth of Focus = 0.4 um. Two optical steppers are available with the following specifications:

#### NΑ

Stepper AK65 nm (I-line)H.7

Stepper BJ48 nm (excimer laser)H.5

Choose which stepper will meet both the minimum feature and DOF requirements? Show all calculations to justify your choice.

(c)

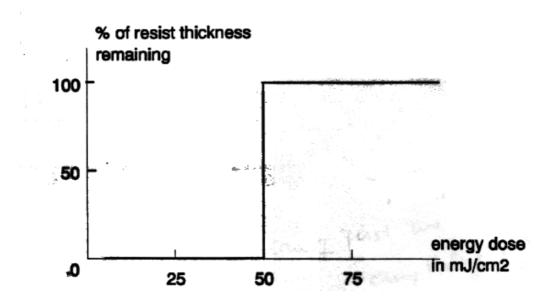

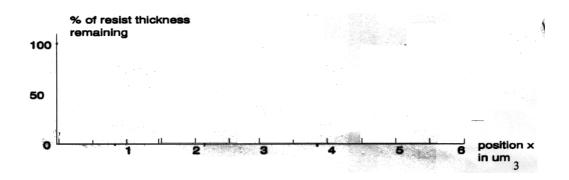

- A. A photoresist has the following response to photon energy dose after development.

- (i) (2 points) Is this a positive or negative resist?

(ii) (2 points) What is the contrast (

$\gamma$  of the resist?

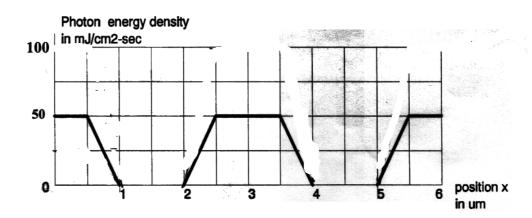

B) The following photon areal intensity profile is illuminated on the resist in part (A). The areal intensity of the photons is expressed as mJ/cm<sup>2</sup>-sec.

(i) (4 points) Sketch below the cross-section of the resist after development with an exposure of 2 seconds.

(ii) (2 points) Sketch below the cross-section of the resist after development with an exposure of 0.5 seconds.

Problem 2 Thin Film Deposition (20 points total)

- (a) A CVD process deposition rate is known to be surface-reaction limited at 700 C was found to be 1000 A/min

- (i) (3 points) Calculate the deposition rate at 800 C by assuming the deposition rate is still surface-reaction limited. [Hint: kT at T=300 K is 0.026eV]

- (ii) (2 points) If the measured deposition rat at 800 C is less than the predicted value of part (i), explain the cause of the devaition in terms of the Grove Model.

- (iii) (5 points) Propose an experiment to verify the explanation you give in part (ii).

- (b) The "Liftoff" Process requires a line-of-sight depostion flux.

- (i) (5 points) Evaporation is a line-of-sight deposition process but is not suitable to practice the "liftoff" process for large diameter wafers. Explain.

- (ii) (5 points) Sputtering deposition with a large sputtering target is suitable for large-area deposition but it not as directional as the evaporation method. How ill you modify the sputtering equipment to make it suitable to perform the "liftoff" process?

Problem 3 Etching (25 points total)

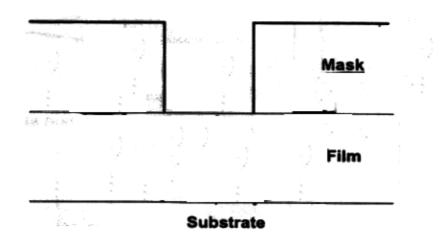

(a) (5 points) The following figure show the cross section of a vertical mask opening over a film. The mask and film have equal thickness. Sketch accurately in the same figure below the cross section of mask and film when the bottom of the film has just cleared.

#### Given:

Etching Selectiveity of film:mask = 2:1 (i.e, vertical etching rate of film = 2

•vertical etching rate of mask)

Degree of anisotropy for mask etching  $[A_f(mask)] = 0$

Degree of anisotropy for film etching  $[A_f(film)] = 0$

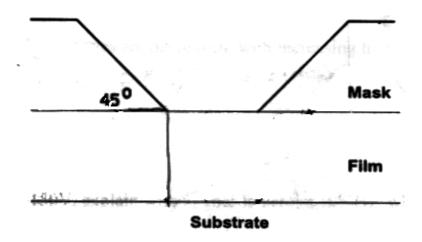

(B) (5 points) The following figure shows the cross section of a tapered maske opening (45 degree) over a film.

The mask and the film have equal thickness. Sketch accurately in the same figure the cross section of mask and film when the bottom of film has just cleared. Also, find the angles of the sloped sidewalss of the mask opening and the film opening.

Given: Etching Selectivity of film:mask = 2:1

Degree of anisotropy for mask etching  $[A_f(mask)] = 1$

Degree of anisotropy for film etching  $[A_f(film)] = 1$

| Angle of the | mask o | pening aft | er etching | = |  |

|--------------|--------|------------|------------|---|--|

|              |        |            |            |   |  |

Angle of film sidewall after etching =

- (b) (5 points) Describe the difficulty to pattern an Al-4%Cu alloy with reactive ion etch (RIE) using a chlorine plasma and suggest two approaches to enhance the RIE etching rate of the Al-4%Cu alloy.

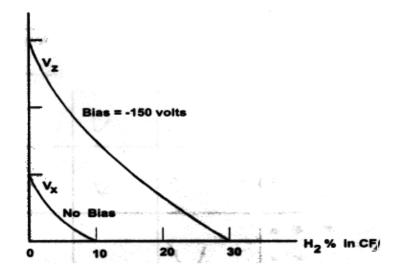

- (c) (2 points) With reactive ion etching of Si, the vertical etching rate  $v_z$  can be enhanced by applying a negative voltage bias to the Si substarte during etching. The lateral etching rate  $v_z$  is relatively independent of the substrate bias. Explain why the lateral etching rate  $v_z$  is independent of substrate bias.

- (d) The etching rate versus etching gas composisiton (a mixture of  $H_2$  and  $CF_4$ ) are plotted in the figure below for (1) vz (bias = -150 volts) and (2)  $v_x$  curve will be identical for all bias voltages.

- (i) (3 points) Explaine why both curves are decreasing with increasing hydrogen content of gas mixture.

- (ii) (2 points) For a bias of -150 V, explain why  $v_x$  goes to zero at 10 % H2 while  $v_z$  is still no-zero.

- (iii) (3 points) for a bias of -150 V and with pure CE4 (i.e, 0% H2), sketch qualitatively the cross-section of a trench etched into Si under this condition. What is the numerical value of the sidewall slope?

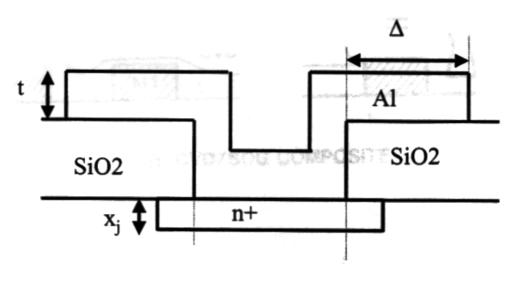

#### Problem 4 Metallization (25 points total)

(a) (7 points) Pure aluminum is used as teh contact metal to a n+/p junction. A sintering step after metallization shows and electrical short to the substrate which is identified to be the "Aluminum spking" problem. In the table below, indicate whether the al-spking problem will improve, worsen, or unchanged (check the appropriate box) if the following process modification are made. Provide a brief explanation.

# p-Si substrate

**Process Modification**

Decrease the junction depth ImprovedWorsenUnchanged

Explanation

Increase the sintering step temperatureImprovedWorsenUnchanged

Explanation

Increase the metal overlap of contact hole

${\rlap{\ }{l}} mproved Worsen Unchanged$

Explanation

Increase the Al thickness t ImprovedWorsenUnchanged

#### Explanation

PECVS a layer of SiO<sub>2</sub> over the Al ImprovedWorsenUnchanged

Explanation

Replace pure Al with Al-1%Si alloy ImprovedWorsenUnchanged

Explanation

Form a metal silicide over teh n+ region before Al deposition ImprovedWorsenUnchanged

Explanation

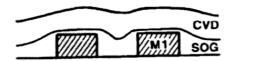

(b) (6 points) The following cross section show two approaches to achieve local planarization of oxide over metal lines with small spacing between. SOG stands fro spin-on-glass and CVD is PECVD oxide.

B: CVD/SOG COMPOSITE

Re-sketch qualitatively the two cross sections below if the metal-metal spacing is 3 times larger (with metal width and metal height being the same).

- (c) (5 points) What is the electromigration failure for interconnets? How do we imprve the electromigration reliability of interconnects?

- (d) (7 points) Sketch the cross-section of a state-of-the-art, planarized, multilevel metallization scheme for integrated circuits using copper as the interconnects. Label all material layers and the methods of deposition and patterning.